Hi Team,

The datasheet shows the following about the condition of detecting a loss of synchronization.

However I couldn't catch the content (yellow part) cleary.

-----------------------------------------------

SYNCHRONIZATION REQUIREMENTS

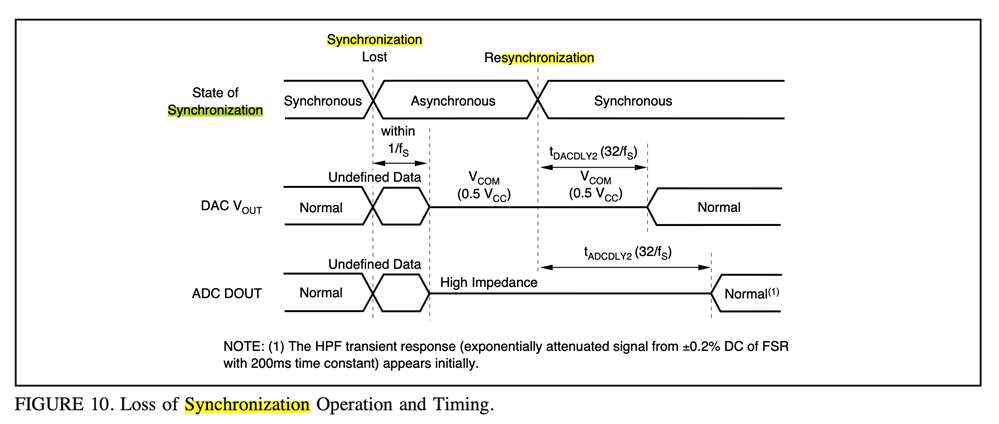

The PCM3500 requires that FS and BCK be synchronous with the system clock. Internal circuitry is included to detect

a loss of synchronization between FS and the system clock input. If the phase relationship between FS and the system

clock varies more than ± 1.5 BCK periods, the PCM3500 will detect a loss of synchronization. Upon detection, the

DAC output is forced to 0.5VCC and the DOUT pin is forced to a high impedance state. This occurs within one sampling

clock (FS) period of initial detection. Figure 10 shows the loss of synchronization operation and the DAC and ADC

output delays associated with it.

-----------------------------------------------

Does PCM3500 count BCK in 1/fs?

Could you let us know how to confirm the loss of synchronization is occured or not in actual BCK, FS, system clock wave form (timing chart)?

Best Regards,

Yaita

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.