Other Parts Discussed in Thread: TAS5634

Hi,

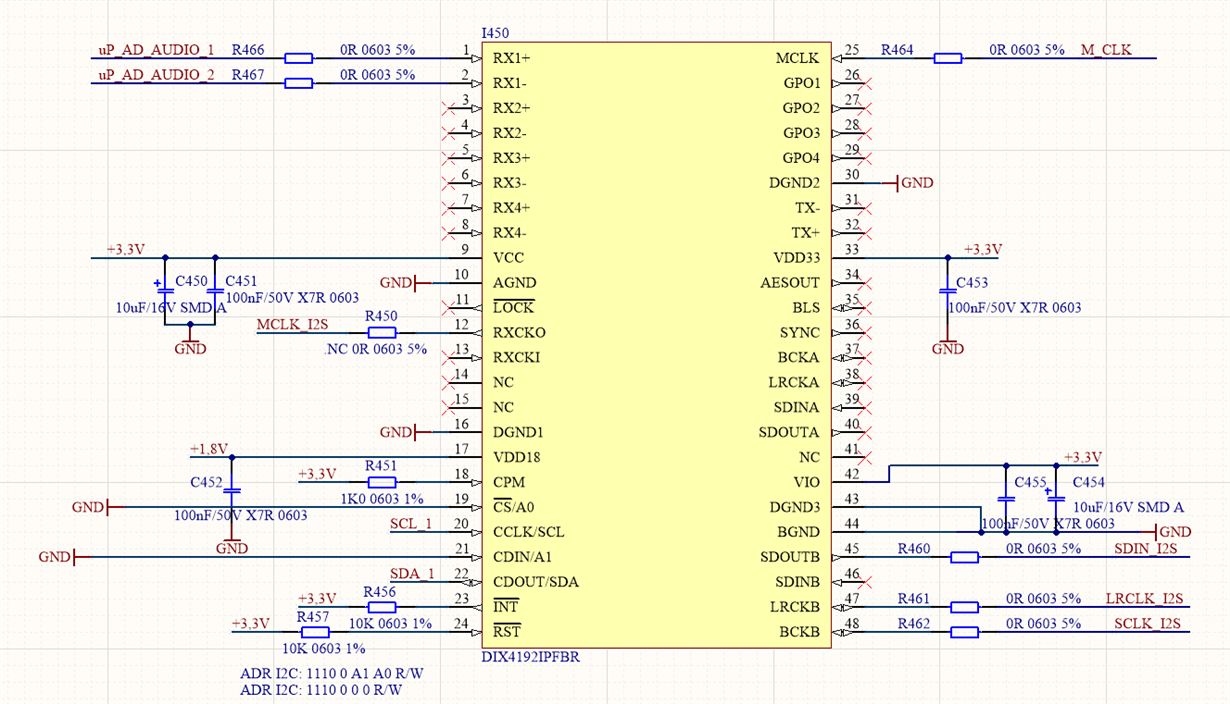

I tried run I2S data via DIX4192. Scheme attached below.

Audio signal input RX1+ and RX1-. I2S data from PORT B (SDOUTB) didnt appear as well as clock from RXCKO. LRCKB and BCKB signals are correct (PWM is generated).

I communicate via I2C:

Address Register value

0x01 0x3A

0x03 0x01

0x05 0x29

0x06 0x01

0x07 0x10

What else registers has to been set?

Thank you very much.

Regards

Vojtech Kana