Hi team,

My customer is using our LM49450 for their headphone design and they have face the phase delay issue which is very similar with a post on e2e.

https://e2e.ti.com/support/audio/f/6/t/819388?tisearch=e2e-sitesearch&keymatch=lm49450

In this thread, you have suggested to set register 0x00 from 21 to 61 corrected the phase delay.

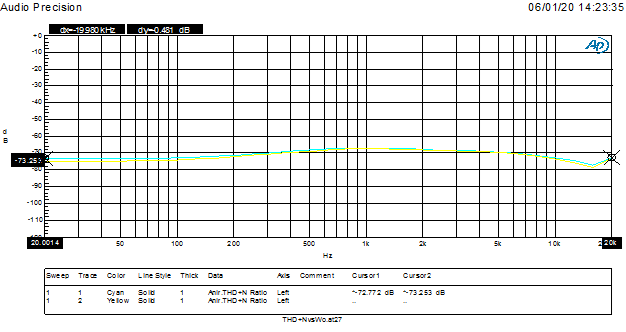

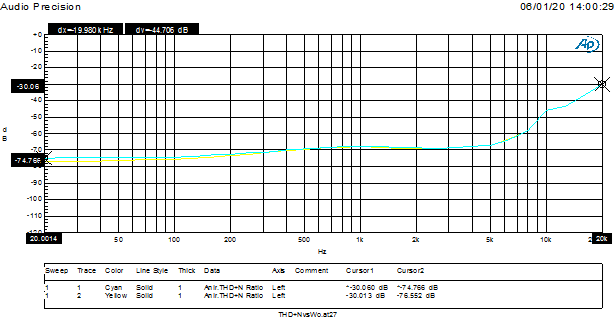

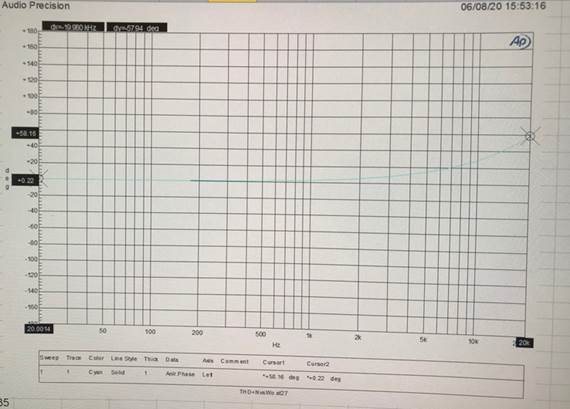

And we also have customer to modify the register 0x00 from 61 to 21. Their phase delay have improved from 5X degree to 28 degree but their THD+n has violate the spec of theirs (>-60db).

So, may I have your help to know how to fix the phase delay issue and also don't influence the THD+n performance? Their fMCLK= 3.079MHz and their register setting is as below. Thank for your kindly help.

Register Addr 0x0 = 0x61

Register Addr 0x1 = 0x0

Register Addr 0x2 = 0x26

Register Addr 0x3 = 0x0

Register Addr 0x4 = 0x0

Register Addr 0x5 = 0x0

Register Addr 0x6 = 0x0

Register Addr 0x7 = 0xb

Register Addr 0x8 = 0xb

Register Addr 0x9 = 0x0

Register Addr 0xa = 0x0

Register Addr 0xb = 0x0

Register Addr 0xc = 0x0

Register Addr 0xd = 0x0

Register Addr 0xe = 0x0

Register 0X00=21H 00100001

Register 0X00=61H 01100001