Other Parts Discussed in Thread: PCM1748

Hello all,

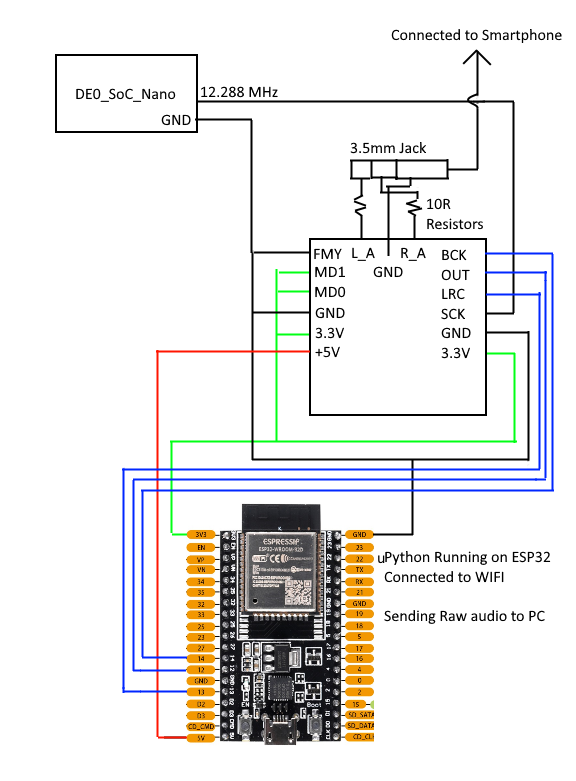

I recently bought a PCM1808 breakout board from AliExpress to get a head start on my university project. For the past week, I have been trying to interface with the PCM1808, to no avail. My first attempt was to use a Cyclone V FPGA to drive the ADC, and relay the audio data to a PC so I could make sure I was driving the ADC properly, but all I get out of it is very loud white noise.

My second attempt this evening was to use an ESP32, with the PCM1808 in master mode (256 fs), with pins MD1 and MD0 set at 3.3 V. This should set the BCK and LRC as output pins, but I am seeing no clocking signal come out of them.

I am beginning to think the chip I bought was a dud, or I have fried it in a way that it still half works.

I have attached images of the clock signals produced by the FPGA when I had it in that configuration. I am pretty confident that the signals are correct, and as you can see, the ADC is outputting data on the DOUT pin, although apparently it is just white noise.

For my University project, I plan to use two PCM1808 and two PCM1748, controlled by a Cyclone V FPGA that sits in the middle, doing audio mixing. It was my false belief that this project would be simple because it was just audio, and yet none of my University lecturers/technicians have never heard of an I2S bus.

The signals in the images are