Hi team,

It is the last issue of the below link. Could you kindly provide some debug direction.

https://e2e.ti.com/support/audio/f/6/p/911258/3371248#3371248

We spend some time to do the test. We also think that it is related with clock structure. Please refer the clock waveform as below.

fMCLK (R18)= 12.288MHz

fI2C_clk (R19)=3.053MHz

fI2C_ws (R21)=48KHz

#2 register setting difference

Register Addr 0x0 = 0x61

Register Addr 0x1 = 0x3

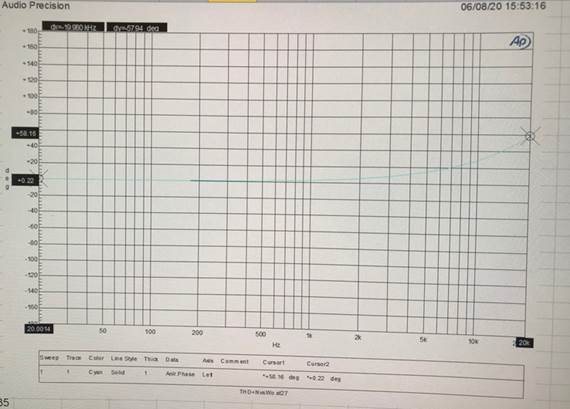

phase delay fail:-58 degree

#3 register setting difference

Register Addr 0x0 = 0x61

Register Addr 0x1 = 0x0

Register Addr 0x2 = 0x49

Register Addr 0x7 = 0x14

phase delay pass:17.96 degree

THD+N Fail : -29.68( Spec>=60dB)

May I know whether there is a setting can pass phase delay and THD+n at same time? Please let me know your recommendation setting and debug flow.

We would like to make the debug flow more efficiency. Thanks.