Hi TI-team

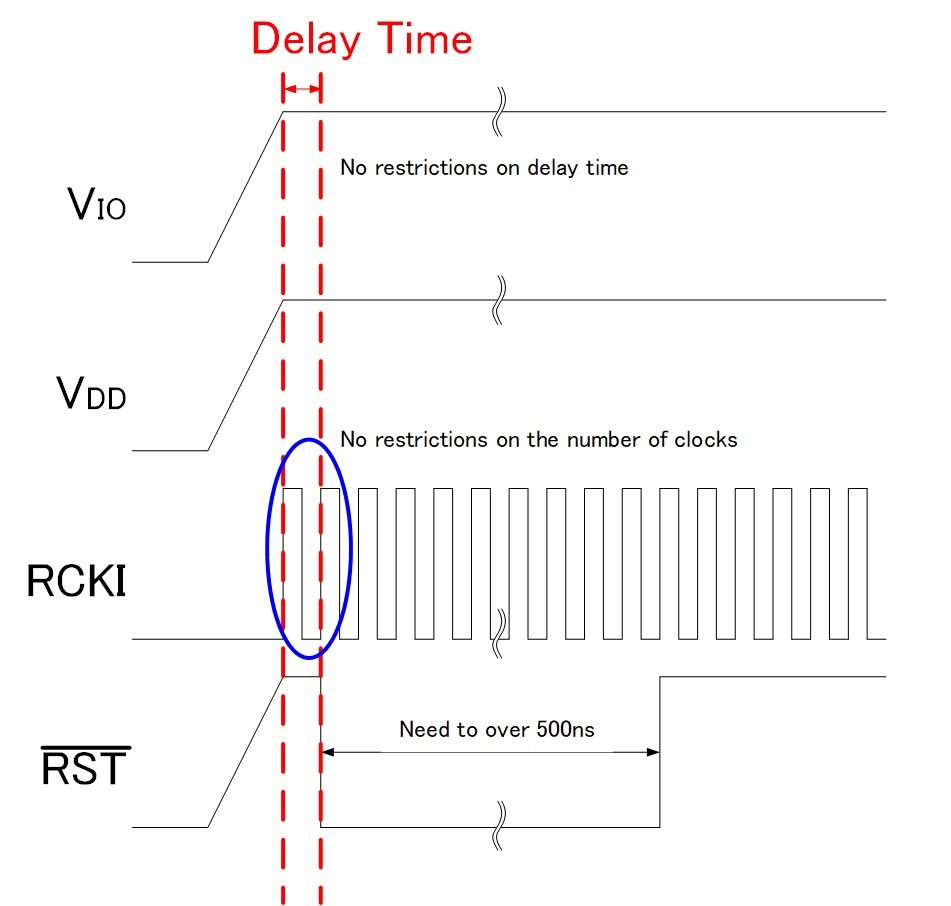

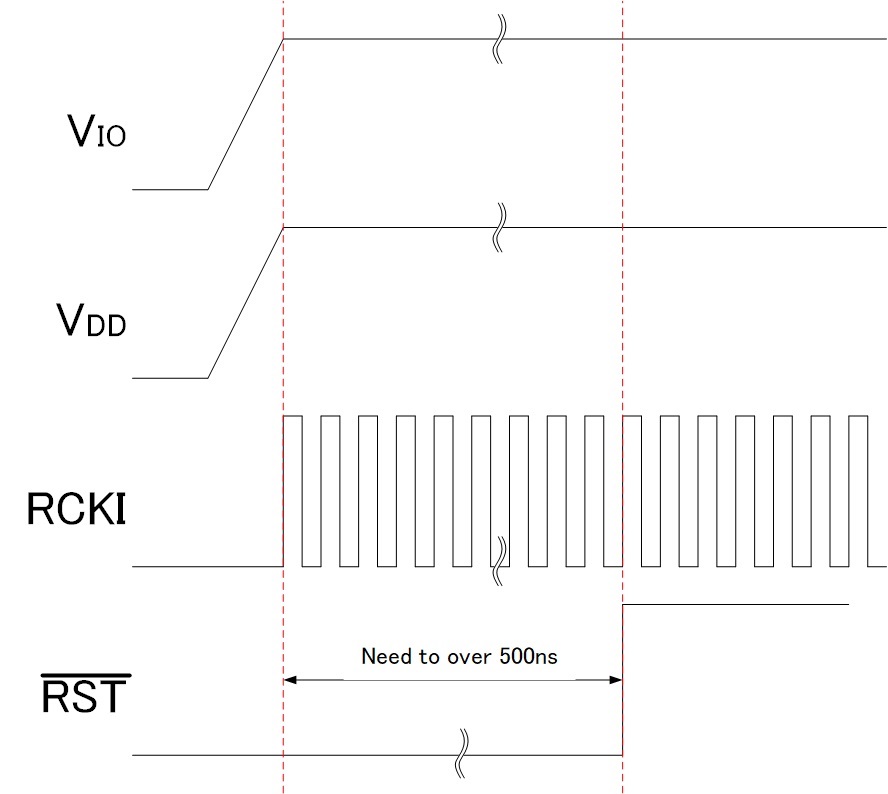

I understand that the RESET period needs more than 500ns.

1. How does the IC behave if the RST(RSTB) is changed from L to H with a time of 500ns or less ?

2.Are there any restrictions on the RST(RSTB) signal rise and fall ?

(Except for clk input in Fig.3 of the data sheet)

For example, a certain amount of time is needed after the rise of VIO and VDD, a certain number of CLK inputs are needed in Fig.3 of the data sheet, and so on.

Best Regards,

Koji Hayashi