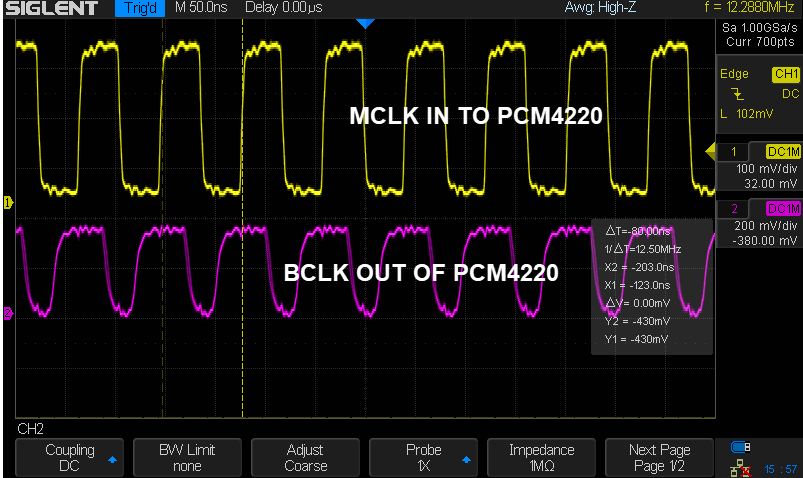

Hi, I'm using the PCM4220 in master mode. Input clock is 50%, 24.576M. In 48K and 96K mode, the output bit clock is 50%, but in 192K mode, the output clock BCK is 69% duty cycle at 12.29 MHz. This is confirmed directly at the pin with all loads removed (jumper is on board right at the pin). The data sheet is really clear that the BCK in "all data formats" should have a duty cycle of 45 to 55% (page 5). With duty cycle at 69% and tdo of 10 nS, it's making data setup very difficult in other parts of the board.

Is this 69% duty cycle BCK expected for 192k?

Some settings: FMT0=1, FMT1=0, OWL0 = OWL1 = 0, SUB0 = SUB1 = 0, DF = 0, HPFDx = 0

Thanks