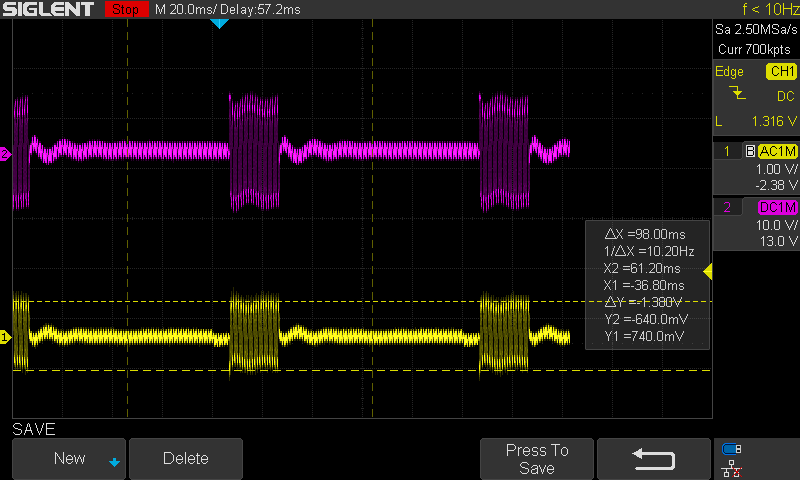

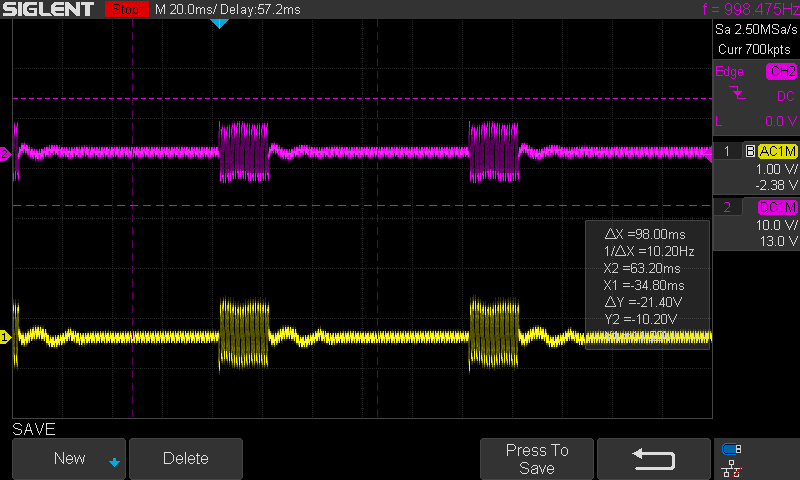

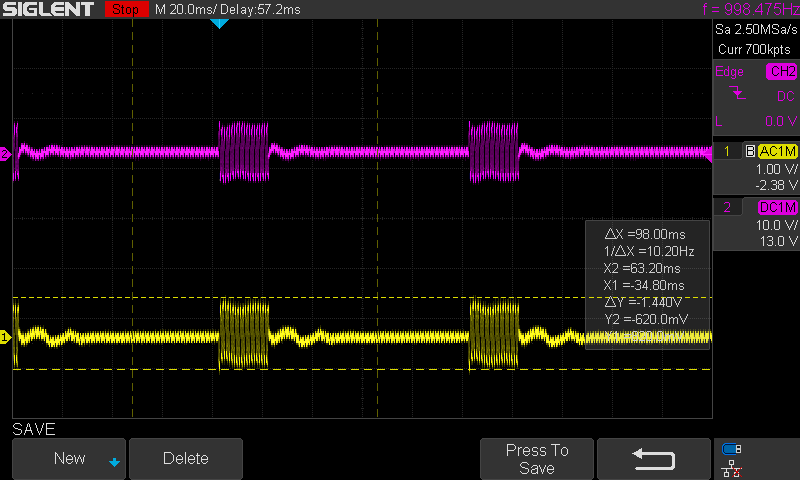

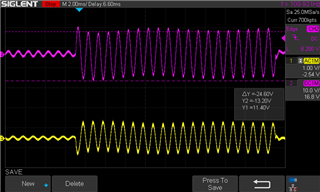

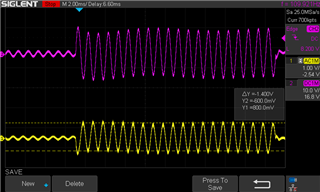

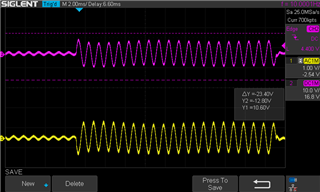

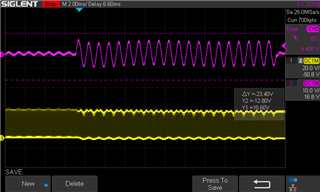

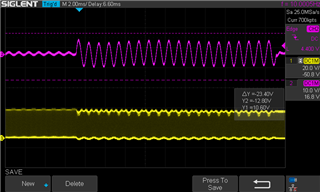

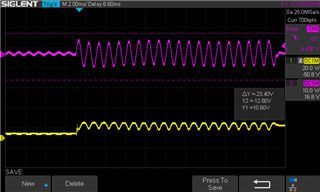

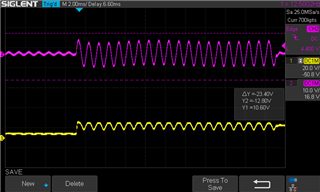

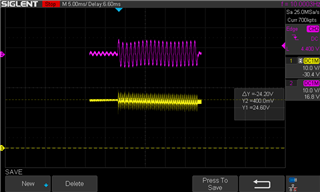

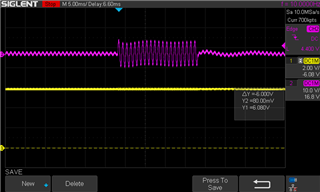

My design using the tpa3126d2 is showing an issue. The output looks good but after playing a few minutes it drops by about 6dB. Input voltages are the same. Doesn't appear to be thermal related. The audio input signal is at the same level. The input is single ended. Checked the GVDD voltage and see no change when the level drops. Any ideas?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.