Other Parts Discussed in Thread: SRC4190

Hi, Team,

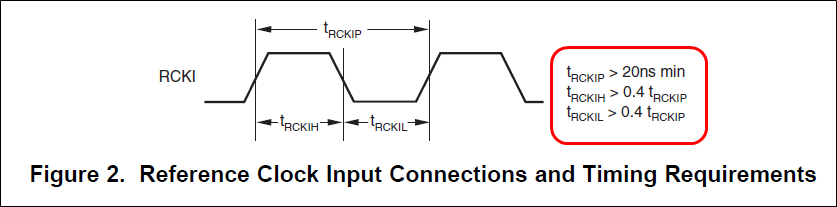

A bit confused about tRCKIH, tRCKIL in Figure 2 of the datasheet because it does not show DC level as well.

Therefore, there are two ways to interpret this:

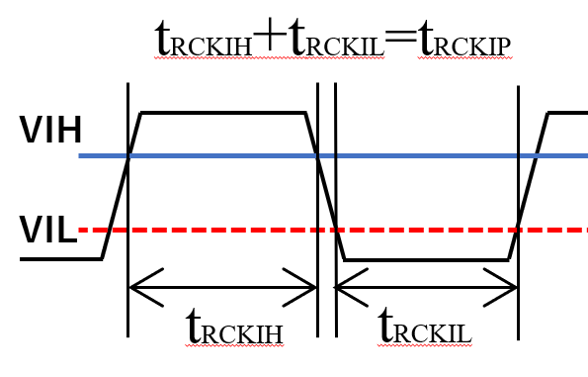

1. From the datasheet, Hi and Lo level voltage is defined as 0.7*VIO, 0.3*VIO, respectively.

Therefore, to be exact, tRCKIH, tRCKIL should be depicted as:

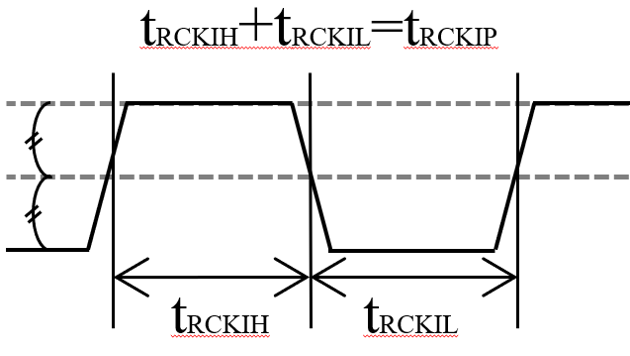

2. Just like depicted in Fig. 2, the border is drawn in the middle of the amplitude.

Could you please tell us the correct understanding?

Thanks and Best Regards,

Masaru Oinaga