hi,sir

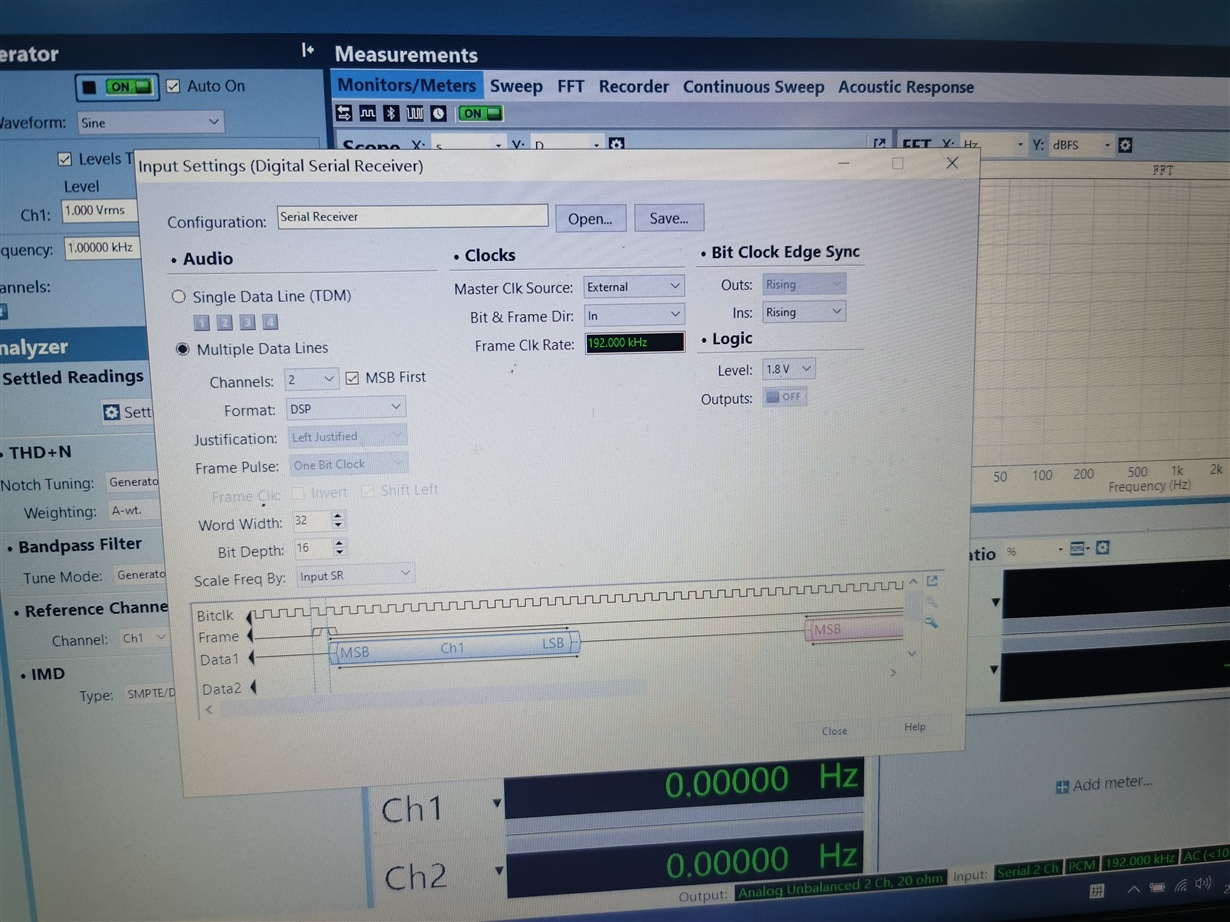

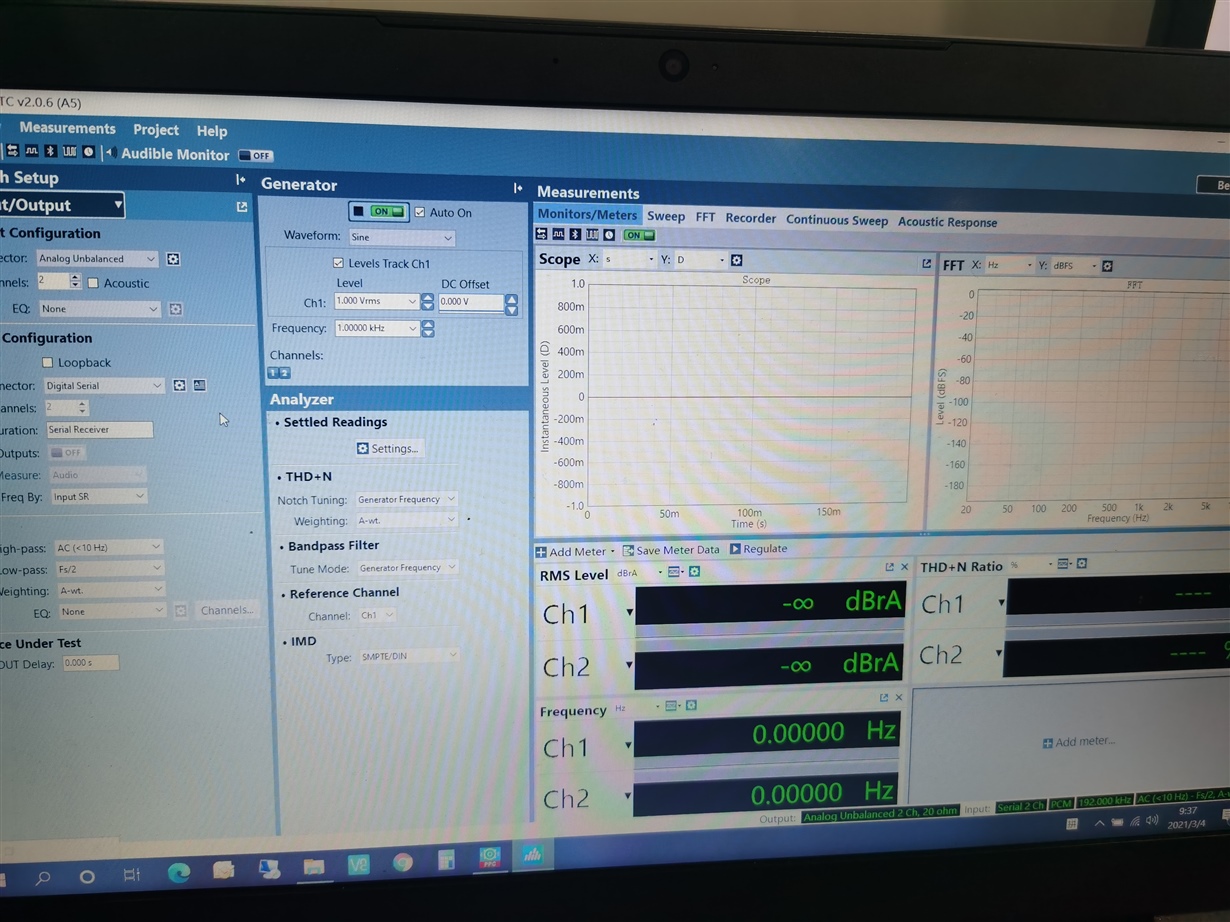

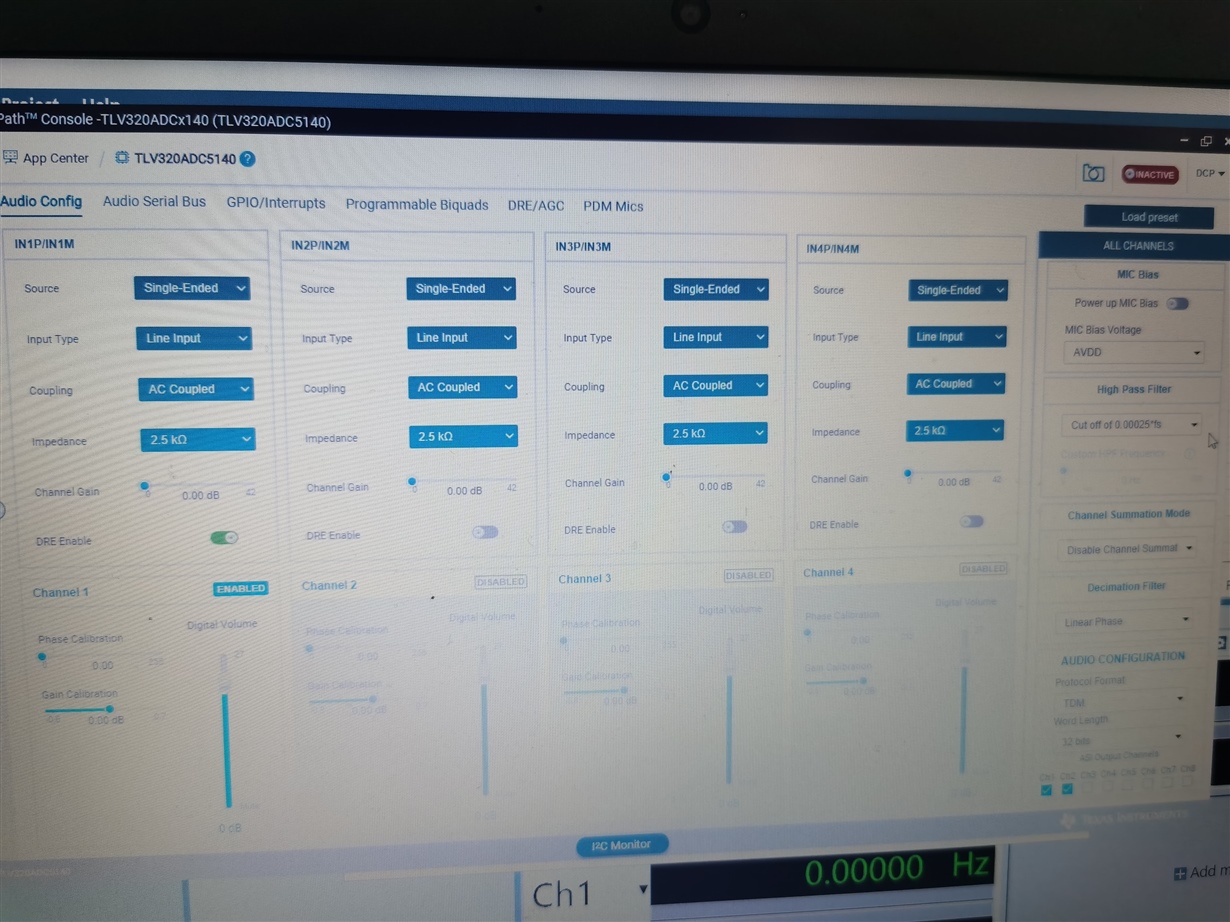

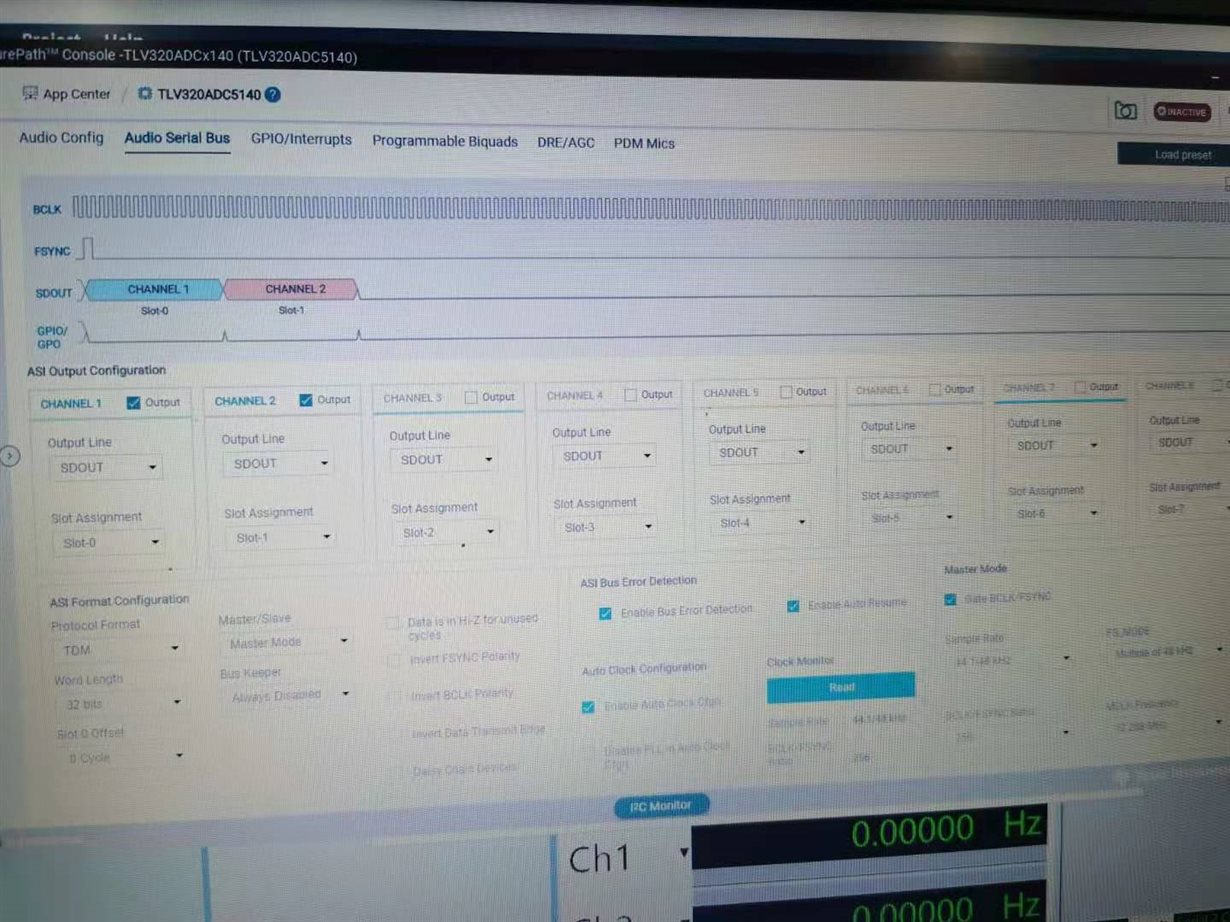

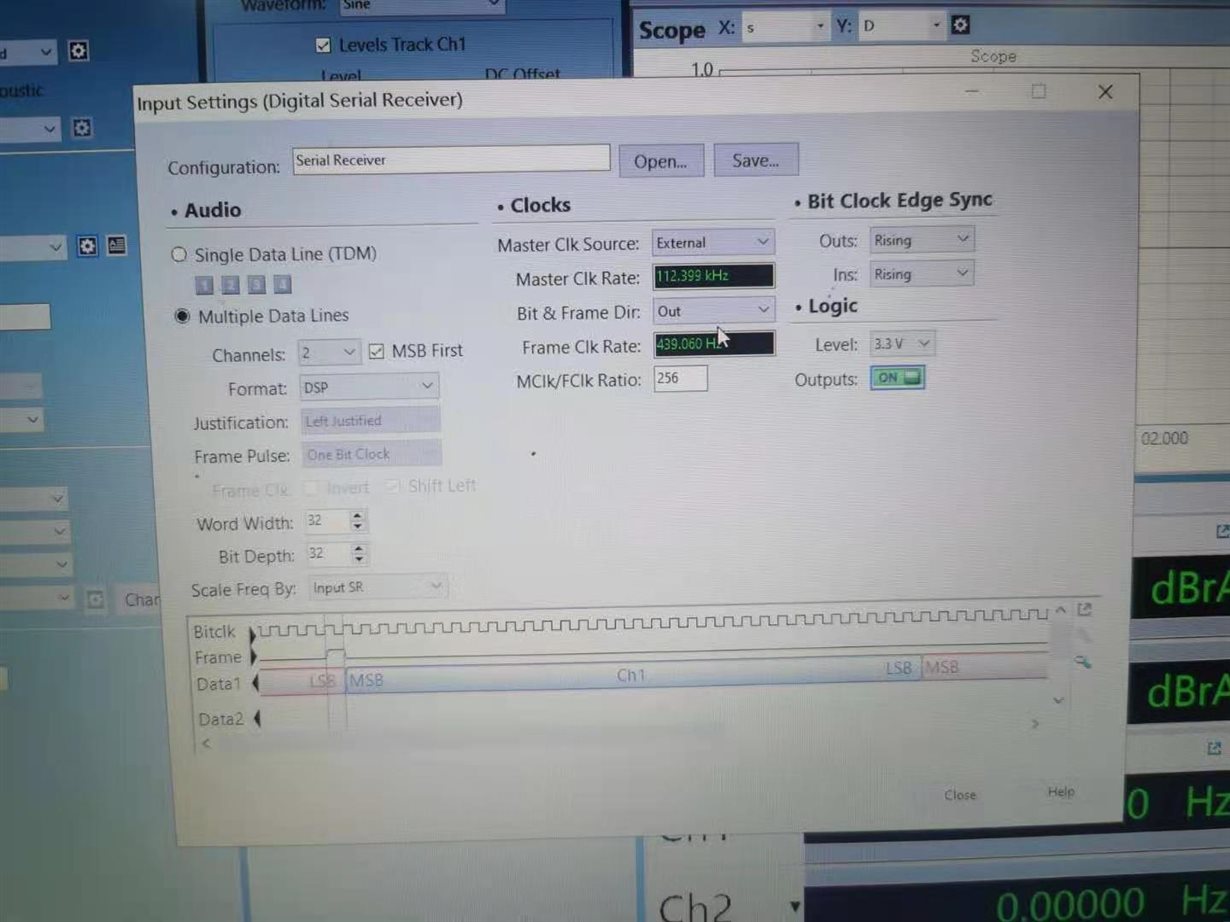

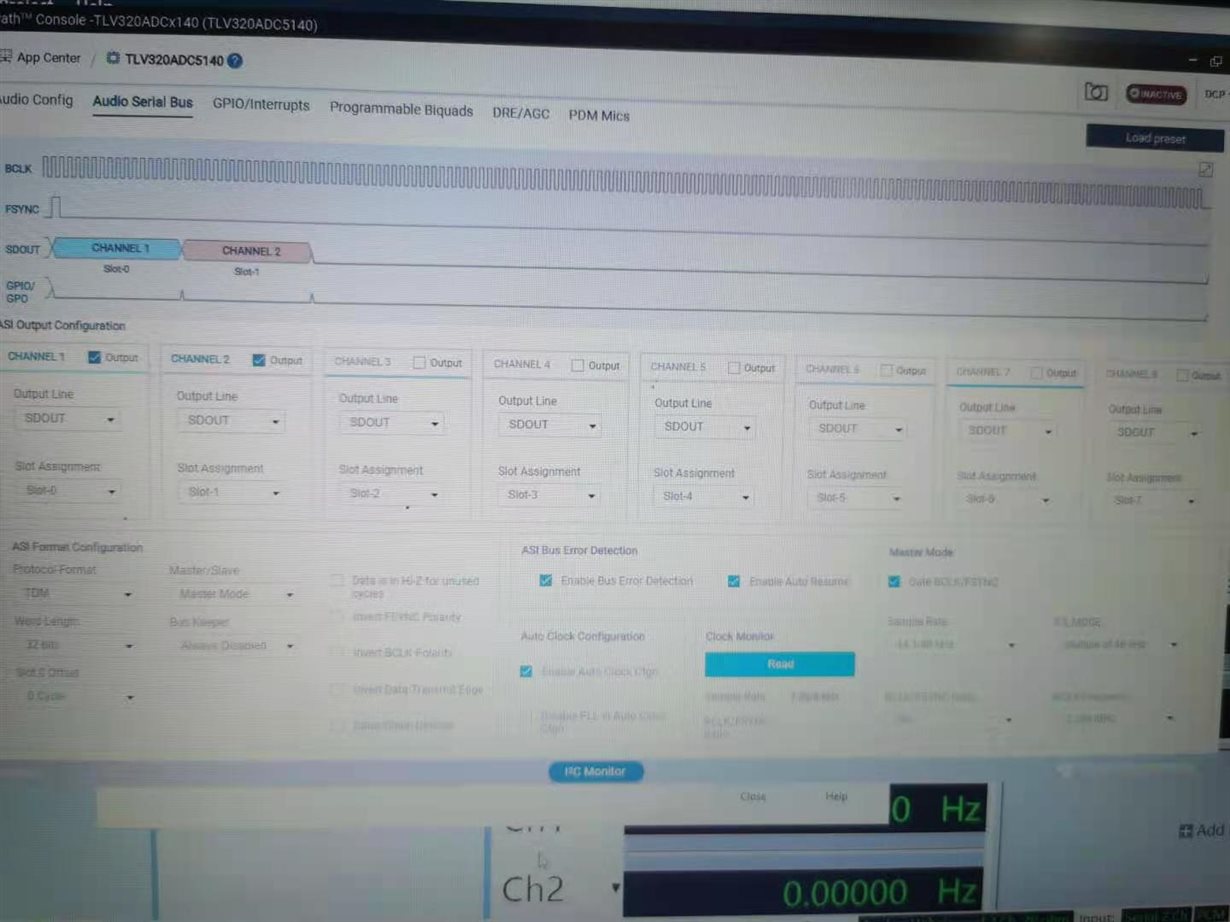

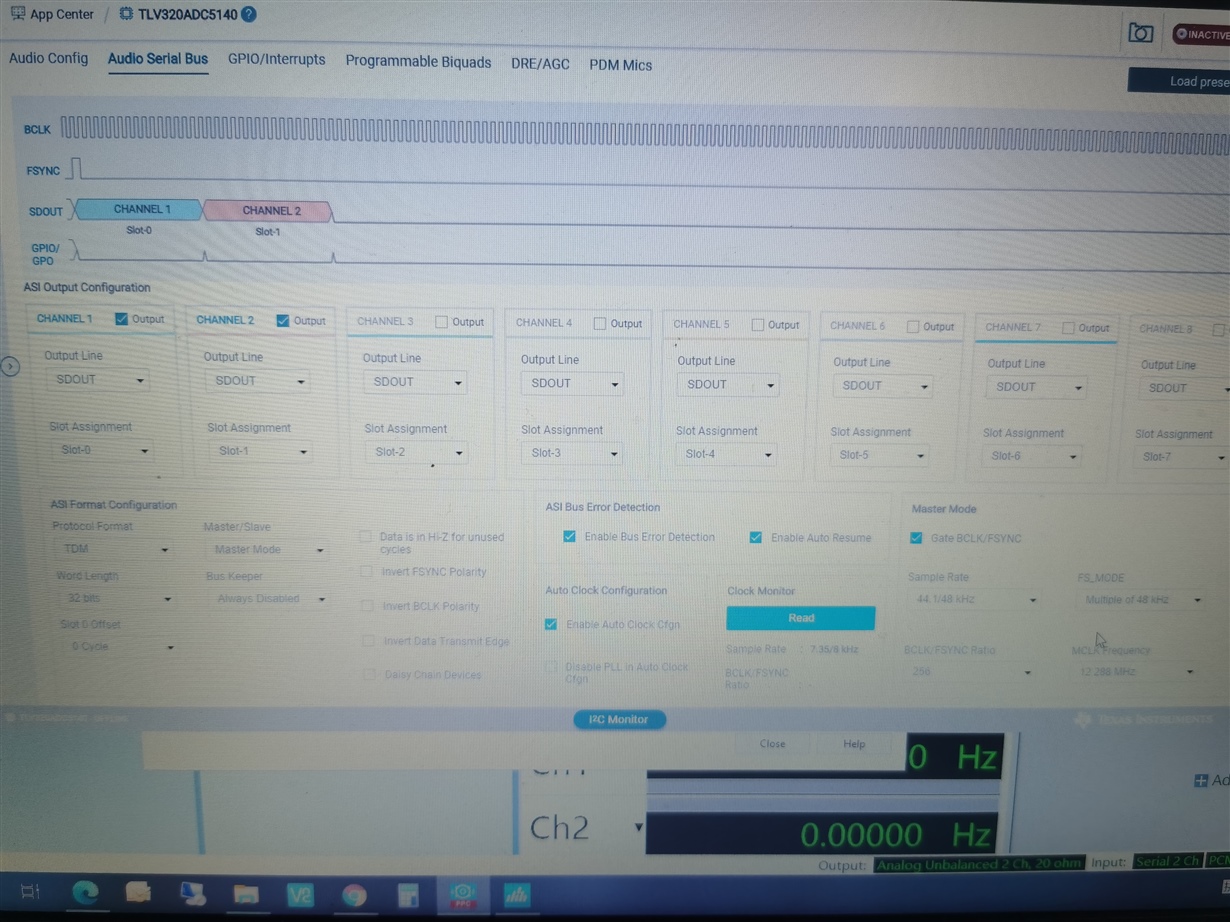

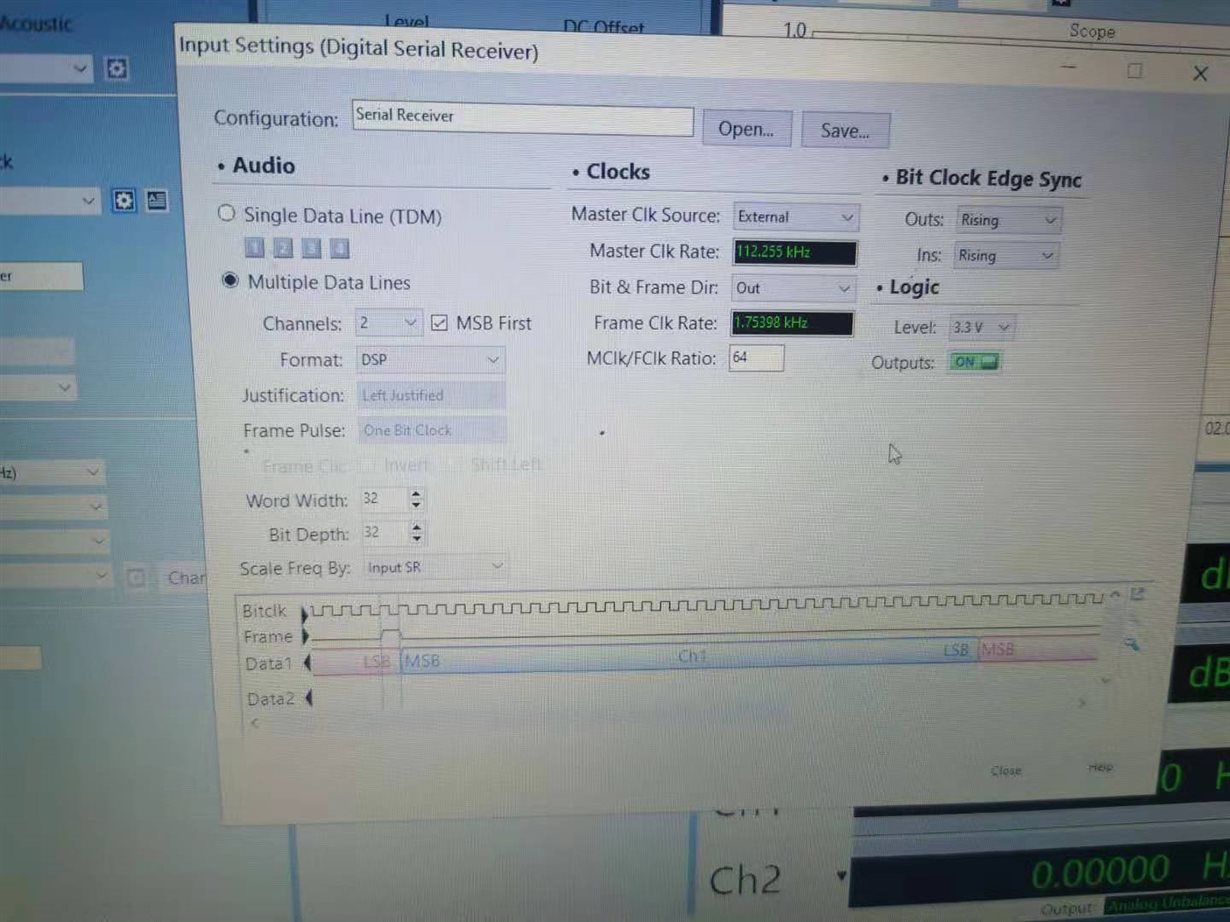

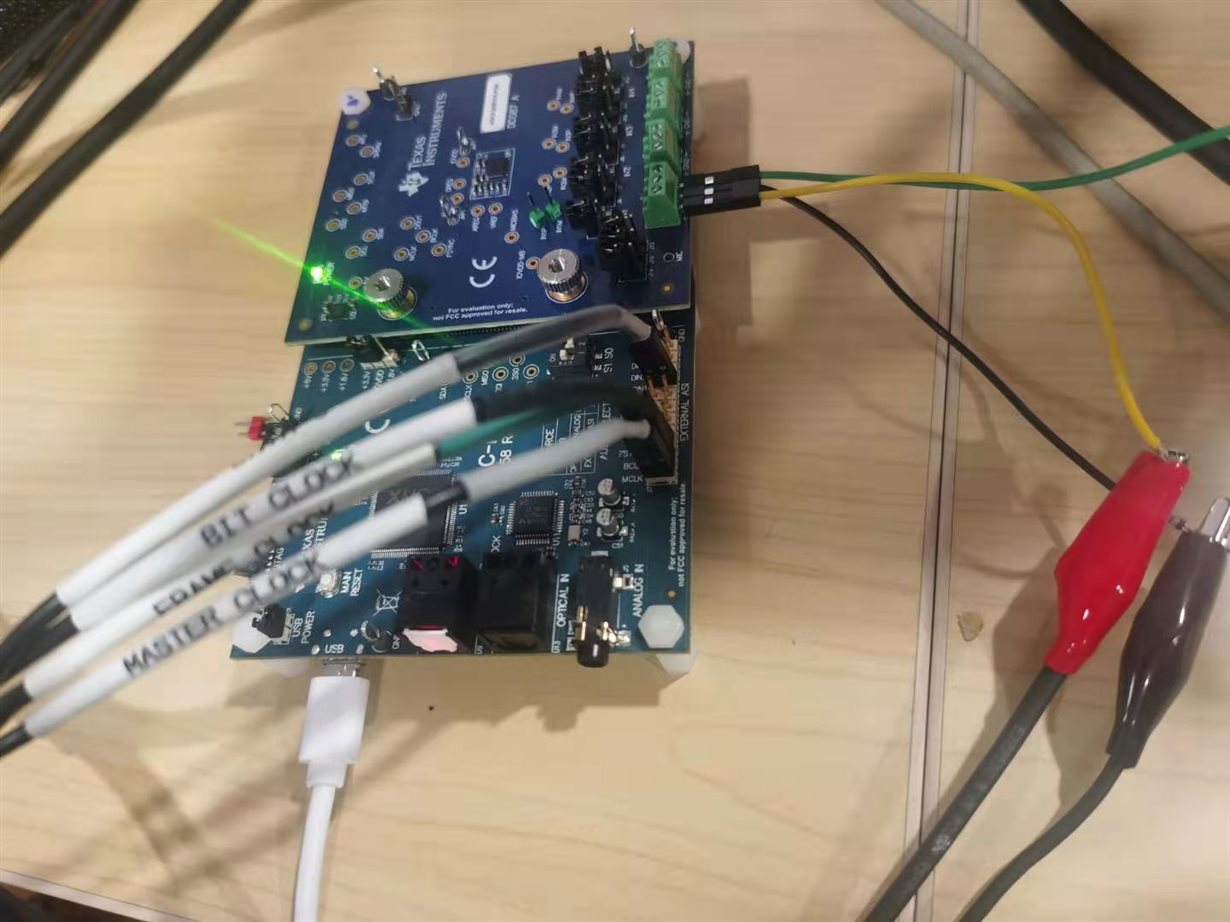

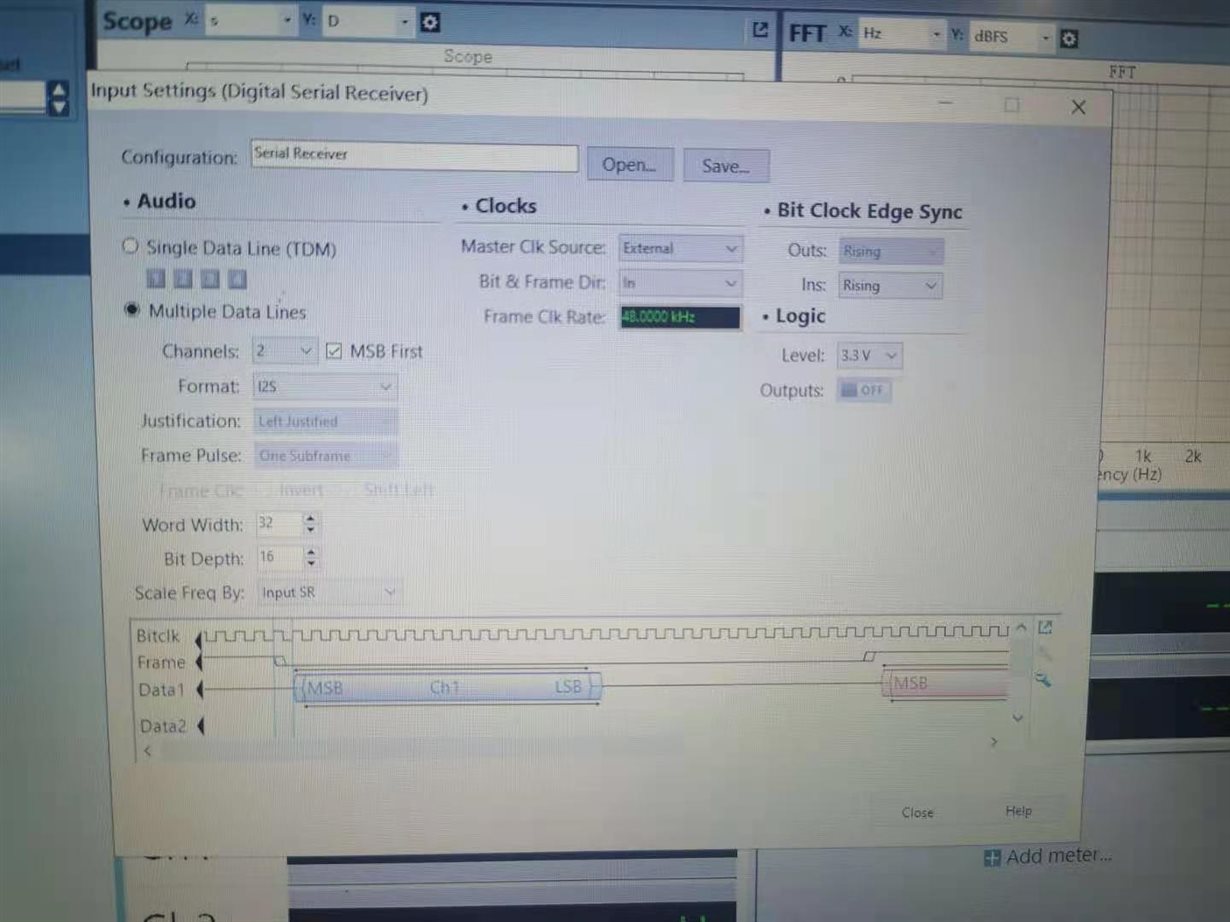

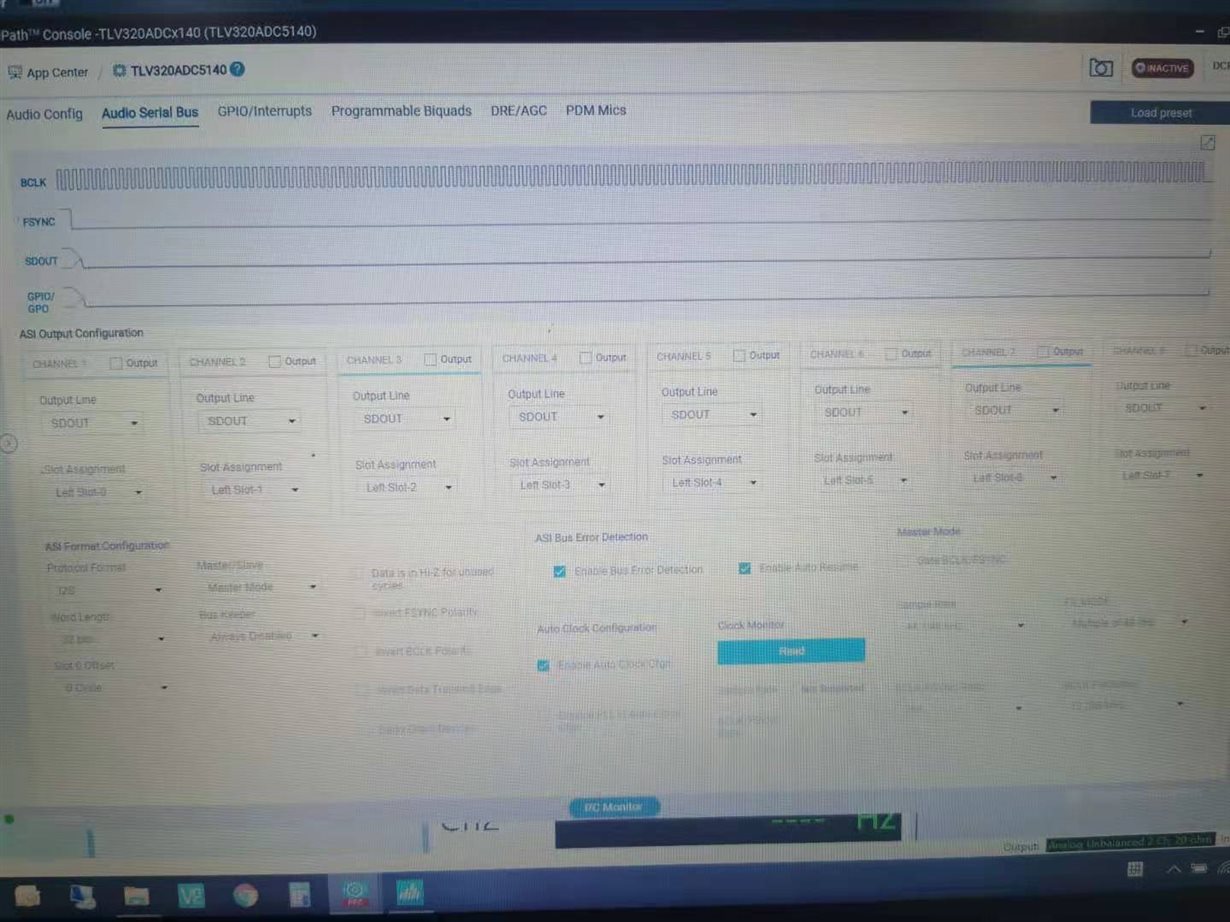

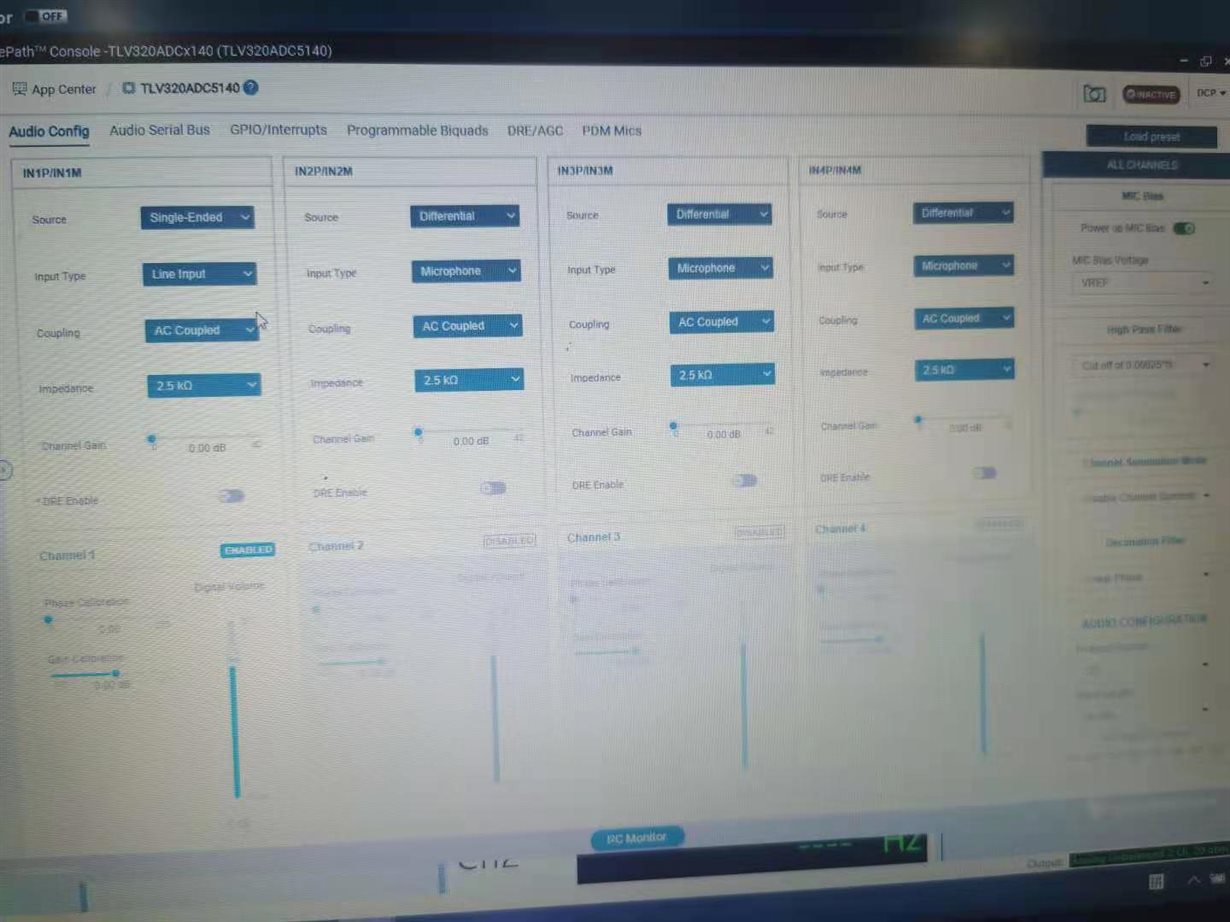

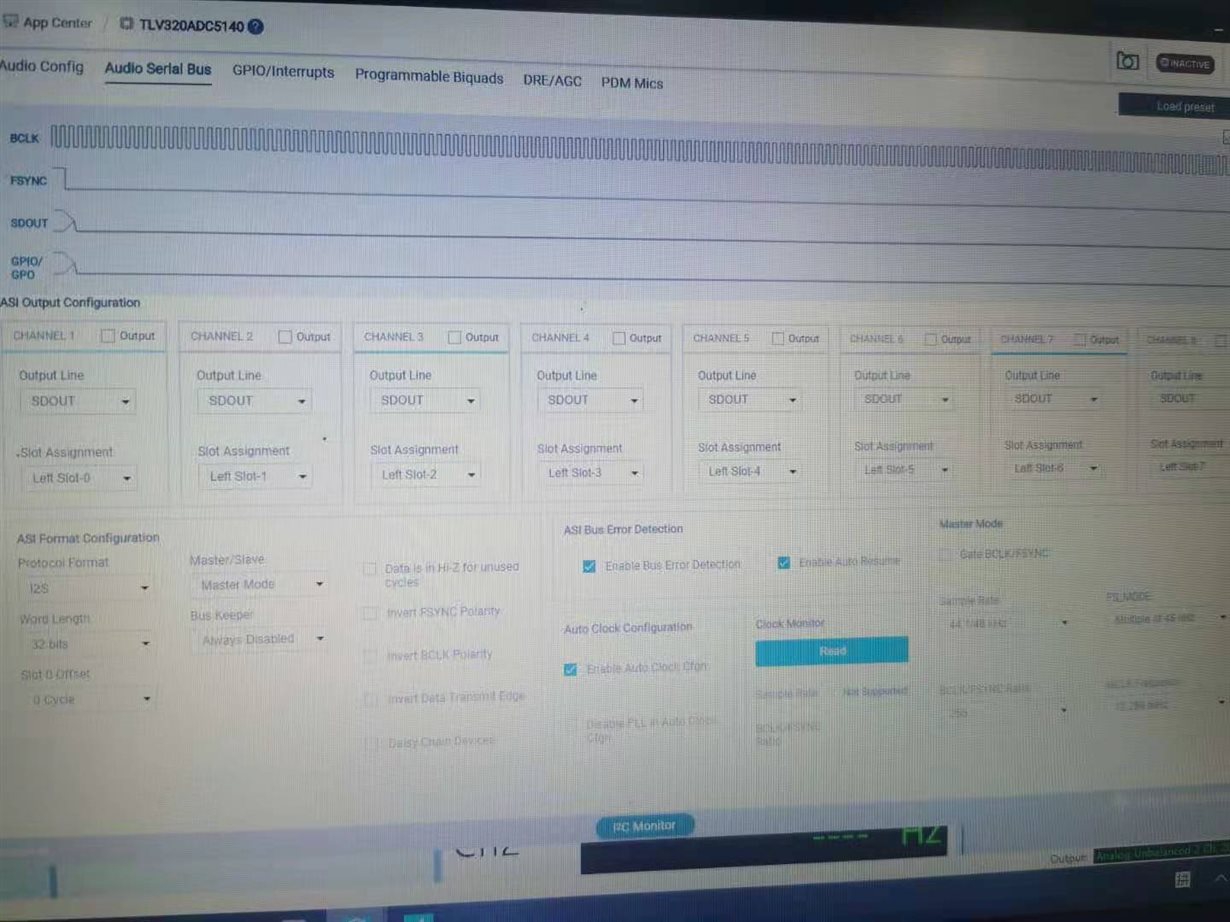

For the above test path, the IIS output of ADC5140 is master and synchronous clock data is sent to AP.

but found the board IIS pin ,have no waveform,i think ,there is ADC5140 config wrong??

please help me check??

clock moniter frame clk not supported,