Other Parts Discussed in Thread: , TAS2562

Hi all,

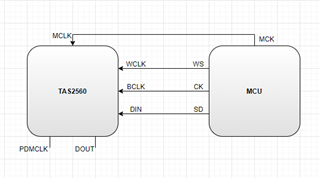

when used in mode 3 (I²S Playback), is it possible to leave the pins PDMCLK and DOUT unconnected and floating?

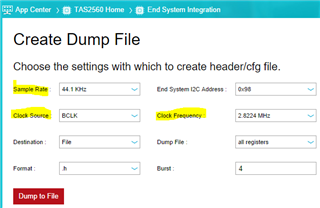

Our product is a docking station for tablets, which integrates a 5 W 4 Ohm full range speaker. We have been recommended the TAS2560 by the speaker supplier. We are planning to use the TAS2560 in mode 3 with I²S playback. Our MCU (STM32F103) provides one I²S, either master/slave, send/receive only. We would like to find good register settings for our speaker with the TAS2560EVM and not do any audio processing in the final product anymore. Does this sound like a reasonable plan?

Best regards

Jakob