PCM1773起動時波形.pdfPCM1773_Audioクロック_HighStart.pdf

Please check two files.

file1:

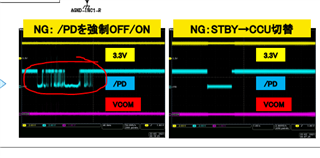

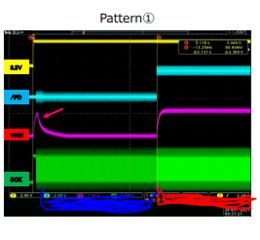

PCM1773起動波形.pdf --> Show customer is getting start up failure on several units. Waveform shows both good and bad case.

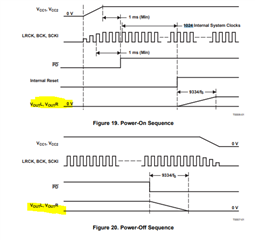

I already confirmed VCC1/2: 10uF + 0.1uf , VCOM 10uF near IC location following datasheet

Customer tried PD hardware RESET but it seems not working. I suppose somthing thermal shudown or another protection was working that why not PD reset did not work. please check the cause of issue and suggest any POR sequence?

File2

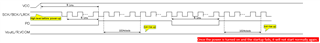

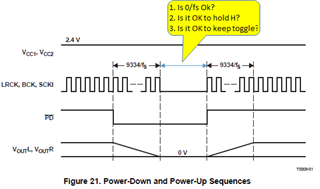

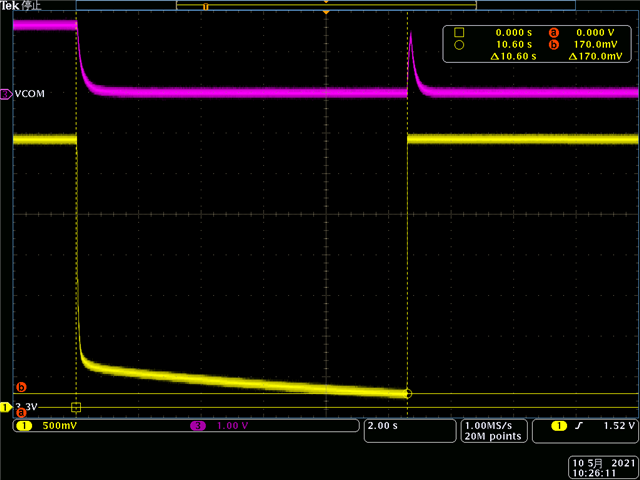

PCM1773_Audioクロック_highstart.pdf

My customer took startup seq waveform as attached. Customer is concerning about Audio clock high start may have been influenced to device function as negative impact. Please check attached waveform and let me know your comment? More detail information or If you have any questions, please let me know.