Hello guys,

I'm a bit at a loss here and I'd appreciate it if you could point me in the right direction or if I've missed something obvious.

I'm working on an ADC -> microController -> DAC project. The ADC is a PCM1804, the micro is an STM32F205 and the DAC is a PCM1793. At the moment the micro is just passing the data between ADC and DAC, a digital wire if you wish. All three are independent boards connected close together. I'm measuring signals with a QuantAsylum400 Audio Analizer, and I can read out the audio signals from the microcontroller over the debug interface. The clock is provided by the microcontroller to both ADC and DAC, both are used as slave devices. The digital interface works. Data comes in, data goes out.

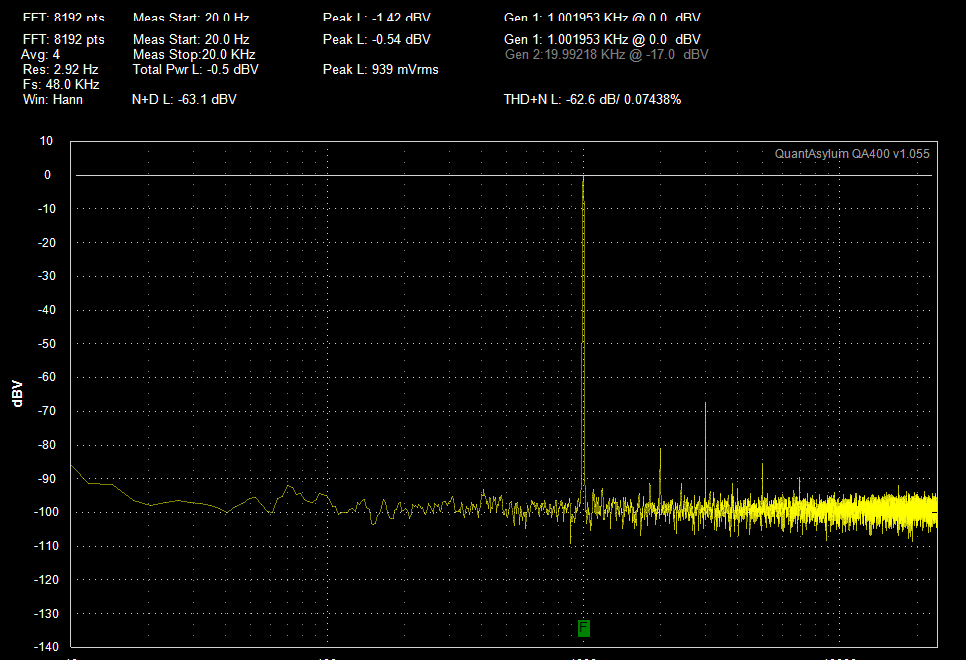

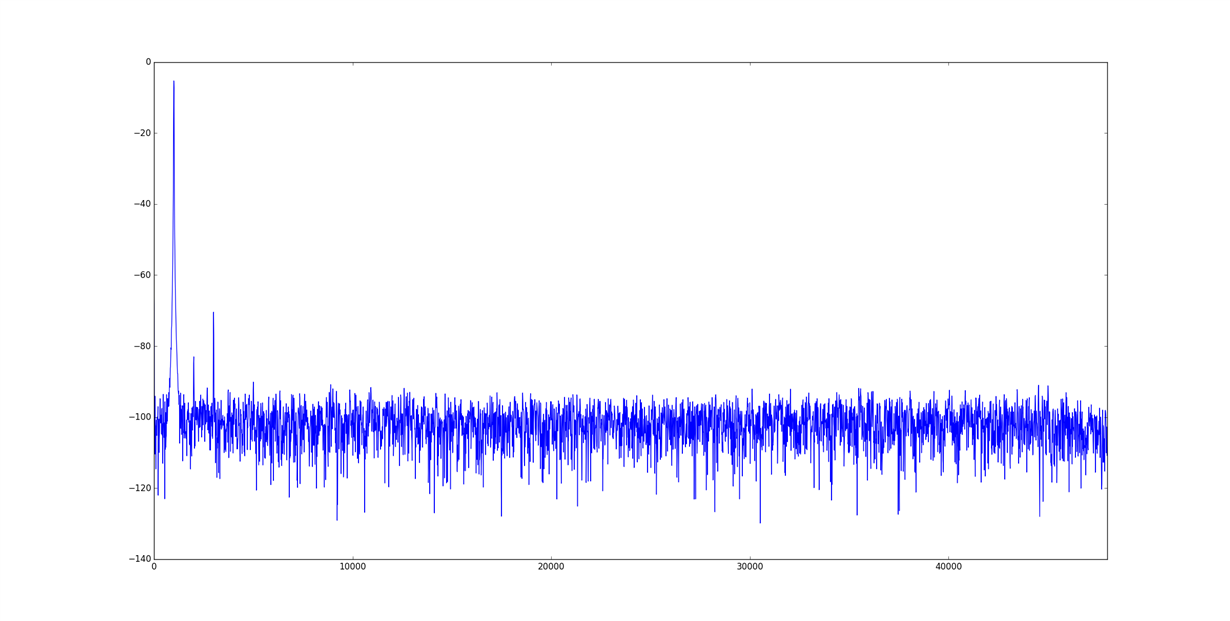

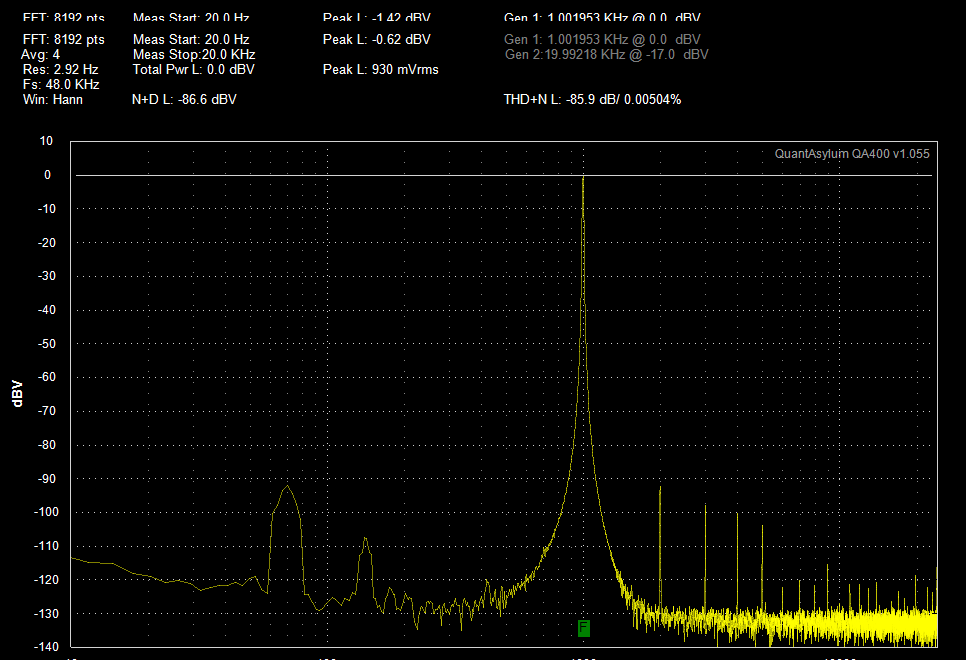

Let's have a look at the DAC output, full scale. The micro generates a 1KHz signal by reading 24bit data from a circular buffer ad infinitum, 96KHz sampling rate, I2S format. The output is 1V RMS full scale (1.41V peak). I'm happy that works fine. There's some minor noise in the 50Hz area, but that's due to the linear regulator on the DC (I think). Anyway, I'm not worried about that.

The output, however, if I pass through a signal from the ADC to the DAC, generated by the analyzer's generator looks very different though. The noise floor is way higher than before (I kept the scale always the same).

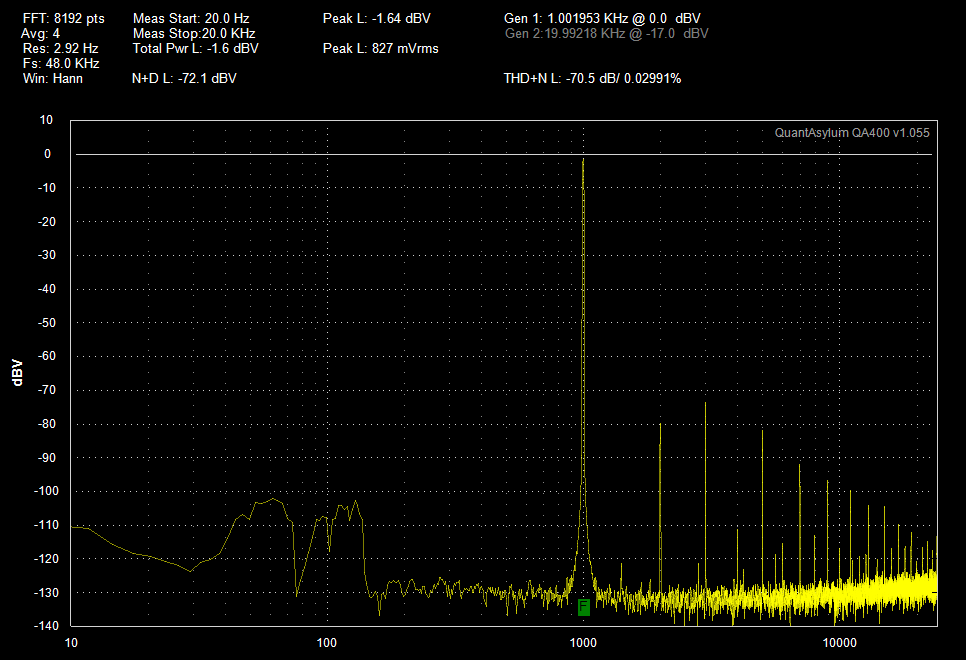

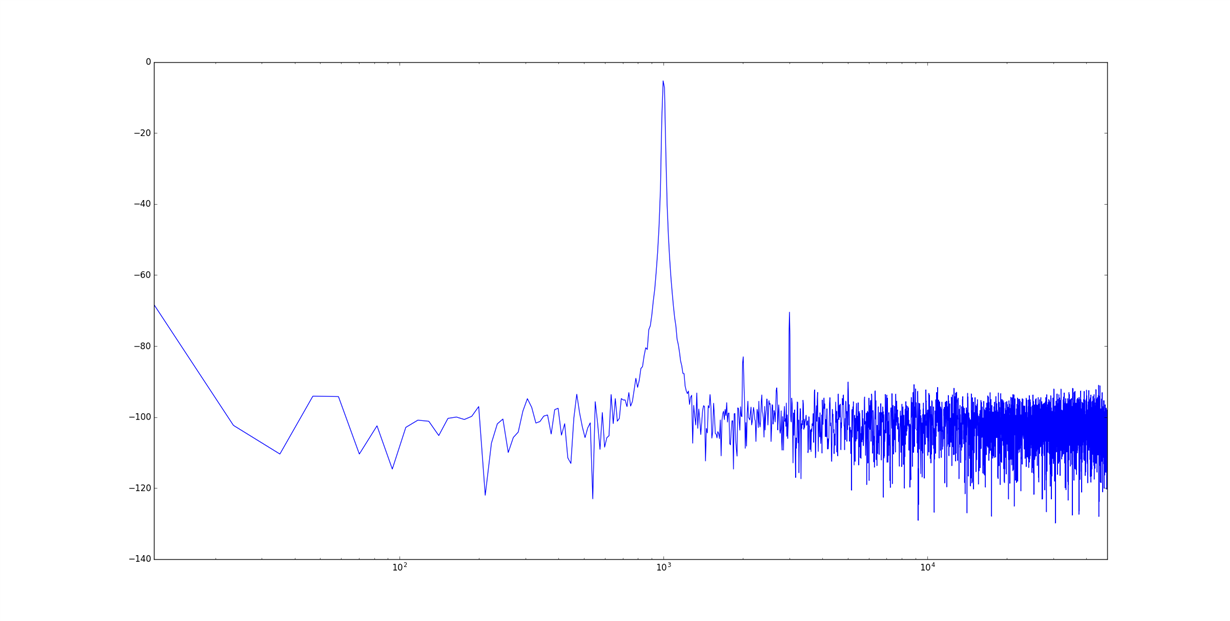

The input to one channel of the ADC, Positive Left (VinL+) looks like this:

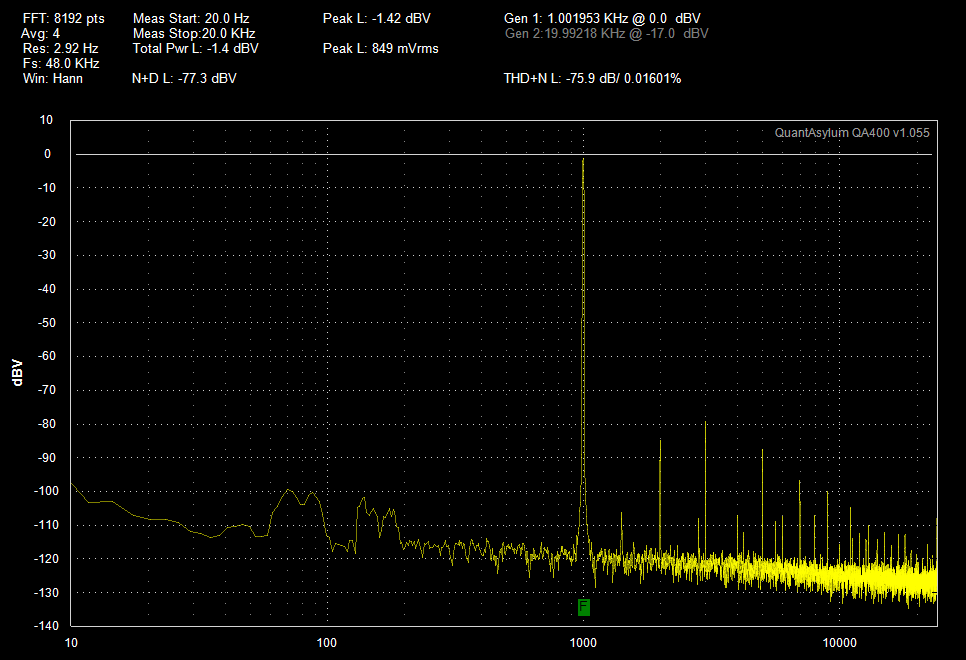

The input on the negative pin of the same channel, VinLeft- :

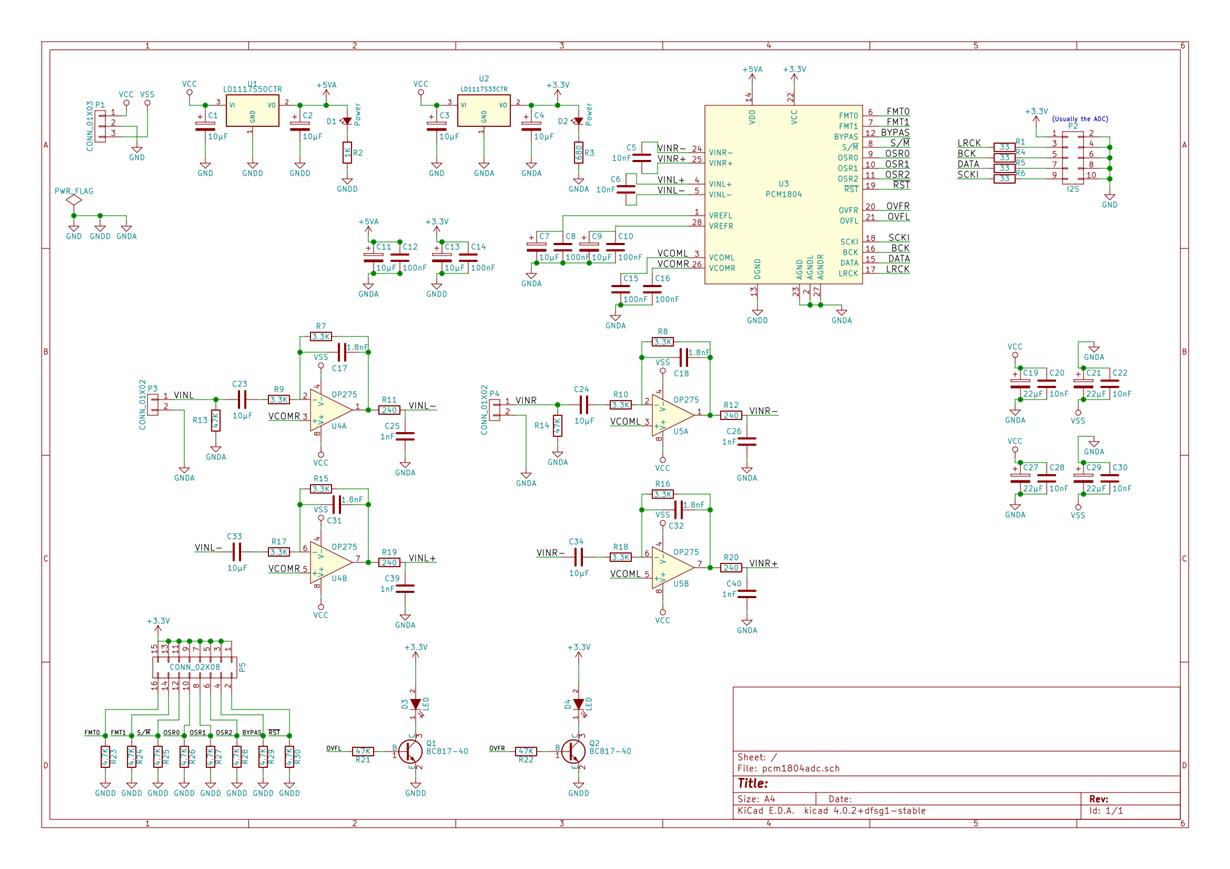

There's some distortion there and artifacts that I'm dealing with, but the input stage is partly taken from the datasheet, and partly taken from Douglas Self's circuit. You can have a look at the ADC circuit here (some capacitor values might have been changed on the input filter), but basically that's it:

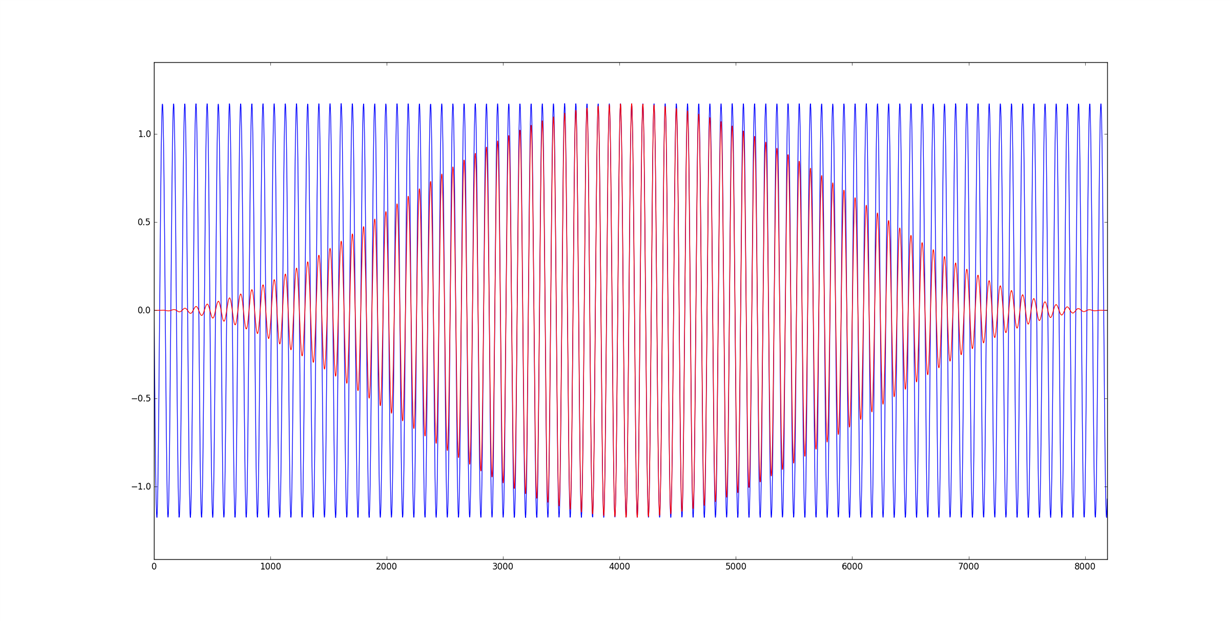

Finally, this is what's inside the microcontroller at any given time (from a memory dump where input audio data is stored, time and frequency formats):

As far as I've checked with an oscilloscope, the FSLK, BCK, and MCLK clocks are good. Settings are OK (FMT0-1, OSR0-2). HP filter is bypassed, slave mode. I tried the same in master mode, no difference.

Am I missing something important? Is this normal on this kind of chip (PCM1804)? I don't expect to get the same performance as in the datasheet, however, this is miles away. I don't think the clock is an issue (jitter?) because the DAC uses the same kind of clock signals, and the result is heaps better, using the same sort of components.

I'm happy to provide you with any more information you need, any help in this case is greatly appreciated!

Cheers,

Albert