Other Parts Discussed in Thread: PCM5100

Please review ( hardware sanity check) PCM5100 schmatic.docPCM5100_output.m4athe attached PMC5100A schematic and listen to the m4a sound file.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Please review ( hardware sanity check) PCM5100 schmatic.docPCM5100_output.m4athe attached PMC5100A schematic and listen to the m4a sound file.

LeCroy3.zipHello Paul,

LeCroy3.zipHello Paul,

Our software engineer, Chuck received the PCM5100 Eval board today. So hopefully this problem will be resolved soon.

I have more data from Chuck and Victor below.

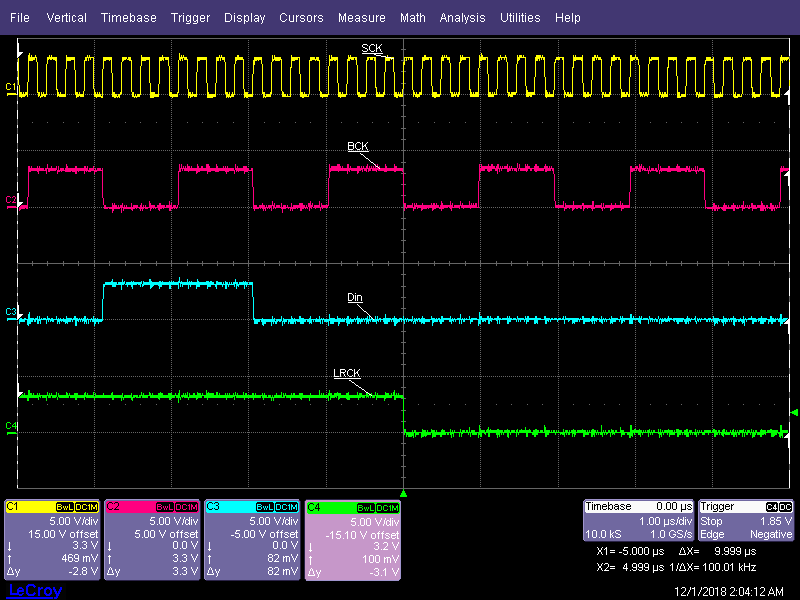

The attached trace file of our problem hardware/I2S bus by color:

YLW trace is CLK

RED trace is BCK

BLU trace is Din

GRN trace is LRCK

I see data coming into Din input (pin 14) and it changes as I press the

K2 button, from periodic blurbs

to continuing signal, e.g. as if a phrase or a tome being outputted.

Yet, the OUTL (pin 6) and OUTR

(pin 7) remain at ground level, as if the PCM5100 is just muted or its output is disabled.

Here’s a synopsis of the digital data being sent to the PCM5100. All signals come from the PIC32.

CLK (yellow) is a high frequency clock (4.096 MHz). This is called SCK or MCK in the PCM5100 spec, but Victor is calling it CLK. It’s OK by me.

BCK (red) or bit clock is used to clock the sample data into the PCM5100, bit by bit. There are 16 bits per sample from a .wav file, originally.

Din (Data In) is the PCM sample data. It is sent according to the I2S standard. There are two channels of data being sent (left and right channel) and each channel contains the same audio data.

LRCK (green) is the Left/Right clock. It tells the PCM5100 when the data for a channel starts by it’s leading edge and for which channel the data is sent according to its level. If high, it’s the left channel, if low it’s the right channel.

The LRCK, BCK and DIN are exactly the same as was sent to the Maxim MAX98357 chip which also supports I2S audio data format. I tested the software before sending it to Victor on our “breakout” board with the MAX98357 and I had good audio at the speaker.

There are actually 2 versions of the software. One version has audio data sampled at 16KHz, the other has audio data sampled at 32KHz. We used the 16KHz data before with the MAX98357 so you may have heard it. The 32KHz data sounds the same from the MAX98357. The traces in the zip file are mostly from the 16KHz version, but a couple from the 32KHz version, I believe. Note that the frequency of the LRCK is always the same as the sampling frequency and BCK is always 32 x LRCK because we are sending 2 16-bit channels of information. CLK is always 4.096MHz and can server either sampling rate.

The reason I added the 32KHz version is because it should allow us to eliminate the need for the CLK. At 32KHz the PCM5100 does not require CLK as an input (just like the MAX98357). This is desirable because it frees up a pin on the PIC32, it has lower EMI emission and makes board layout a bit easier. We’ve decided to go with the 32KHz samples and eliminate CLK, if we can get it to work.

In case you are wondering, the PCM5100 can generate CLK from BCK because it has an internal Phase Lock Loop (PLL).