Other Parts Discussed in Thread: PCM5102A

Dear TI:

Customer used PCM5100A in product, and sometimes PCM5100A no output when it power on, but reset the power, output normal.

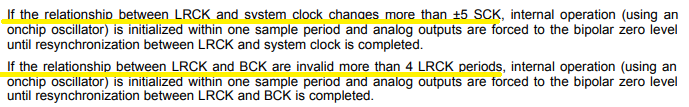

The customer tested and found that there was no output at startup, and the PIN CAPP and CAPM of IC were abnormal, fould the square wave, but the frequency was 880KHz, and the IC frequency of normal output was 1.5MHz. What was the reason for this abnormal?

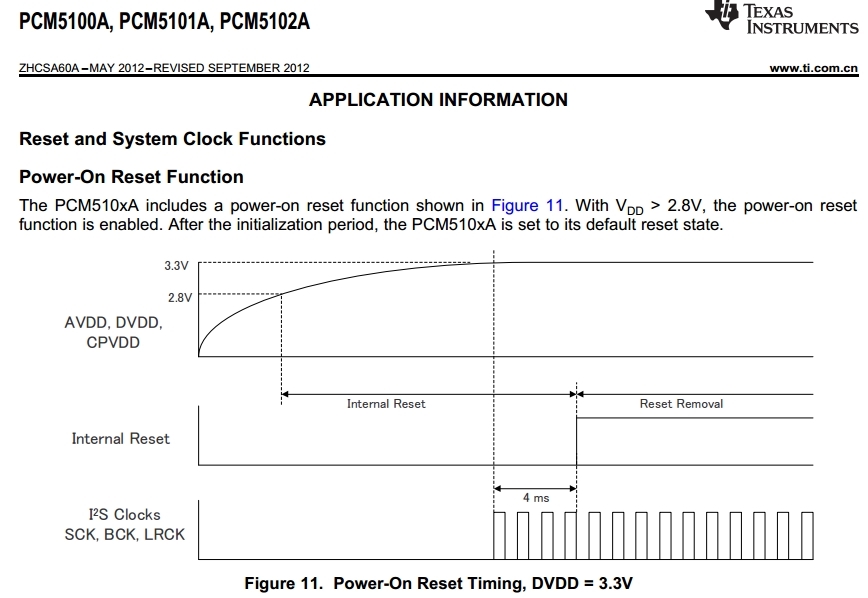

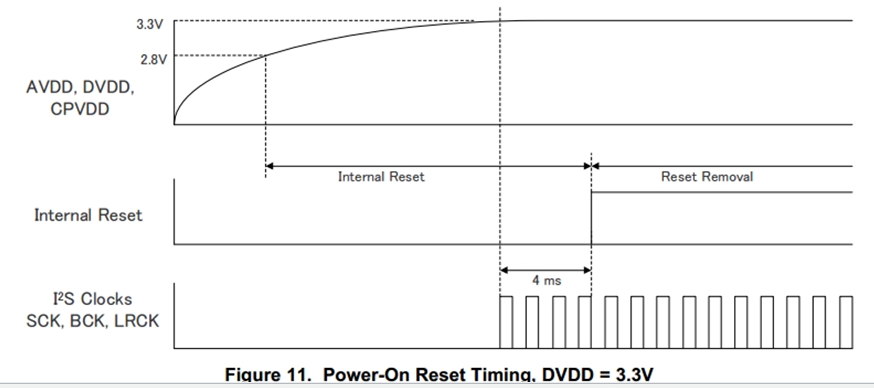

At the same time, do PCM5100A have any requirements for the power timing? At present, the customer set SCK, BCK and LRCK to output first, and then VDD power up. The data of IIS will not be sent out until the power up exceeds 10ms. Is this timing sequence OK?