Dear Ti.

We are having issues with our product which contains the AIC3254 CODEC. The speaker product using the ADC - miniDSP - DAC to provide processing in AUX mode for the speaker. The speaker is efficient and the amplifier has a high-gain but the background hiss is normally at a fairly acceptable level with most devices.

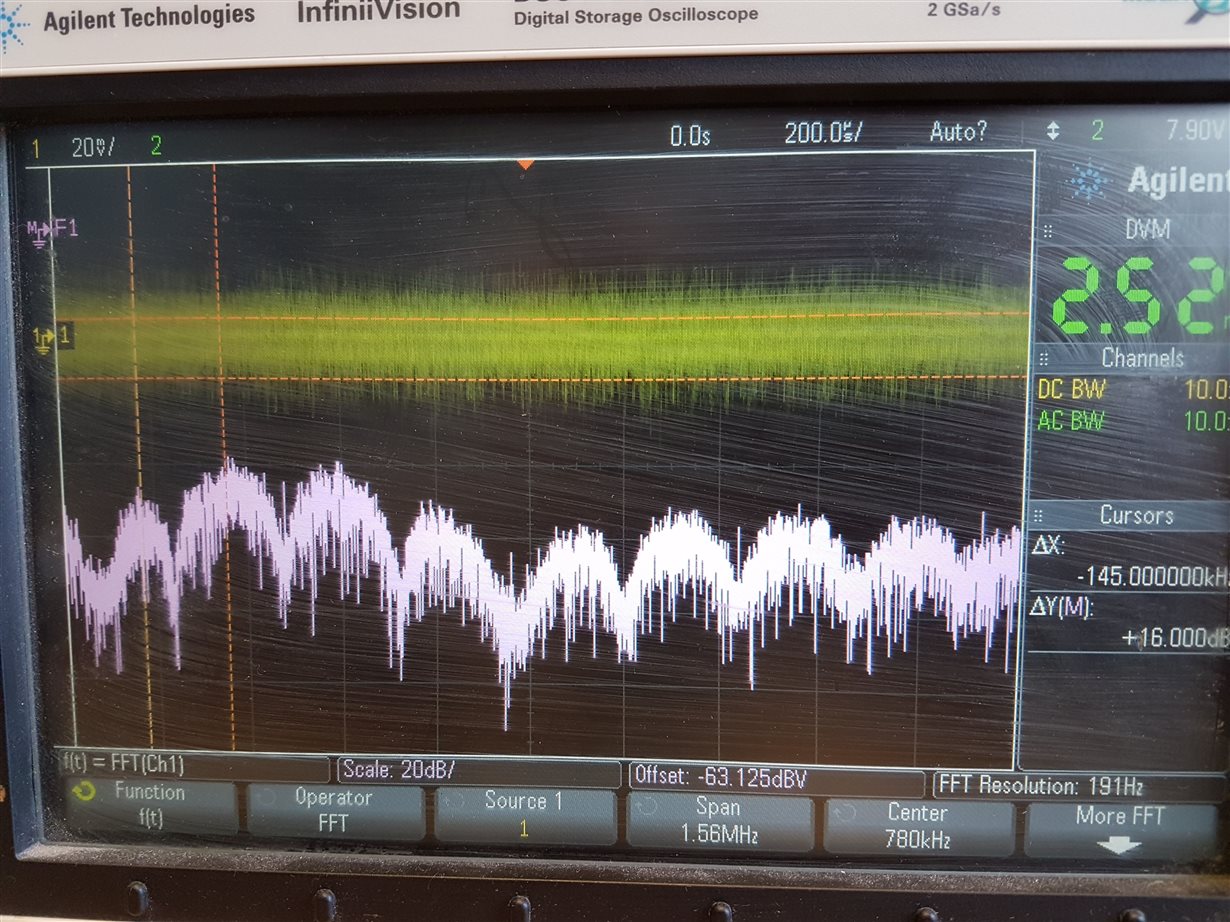

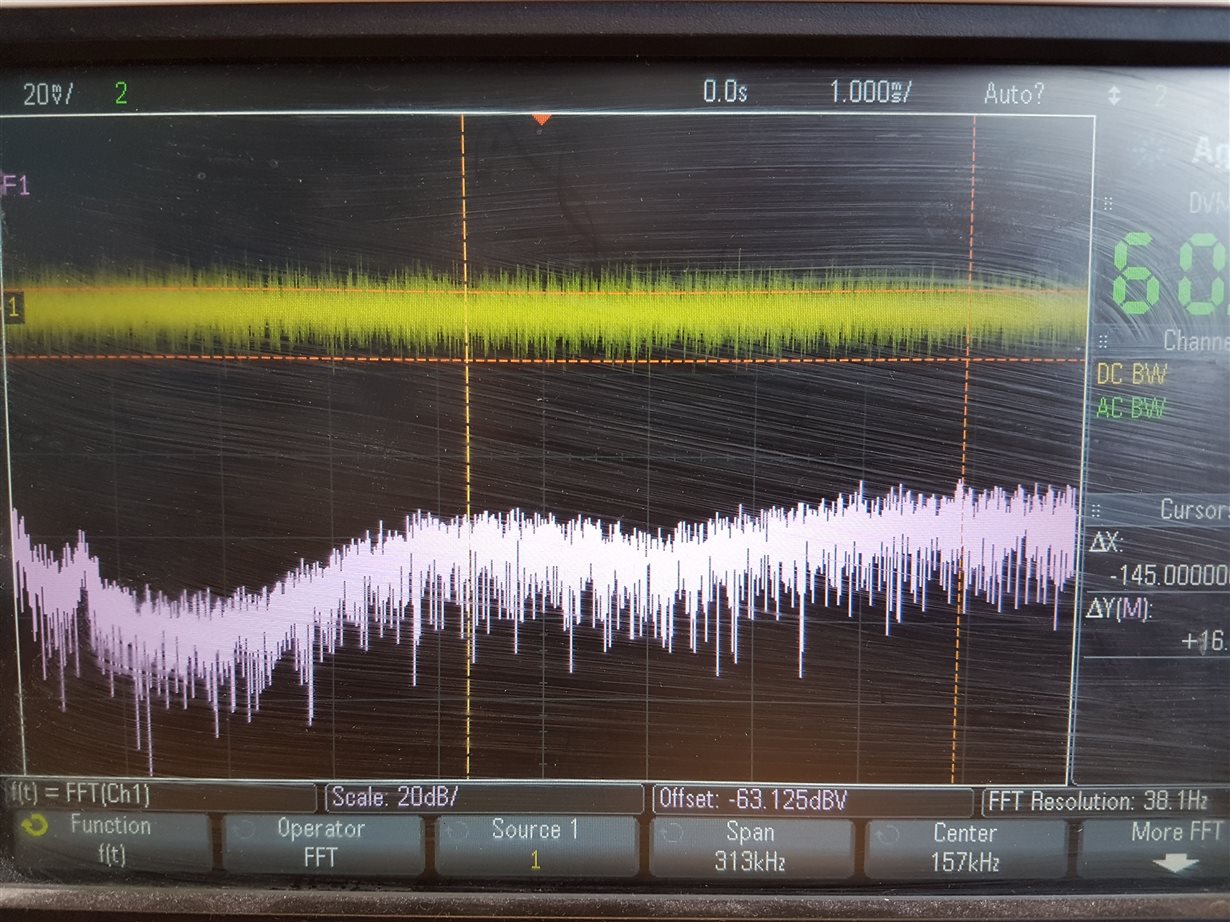

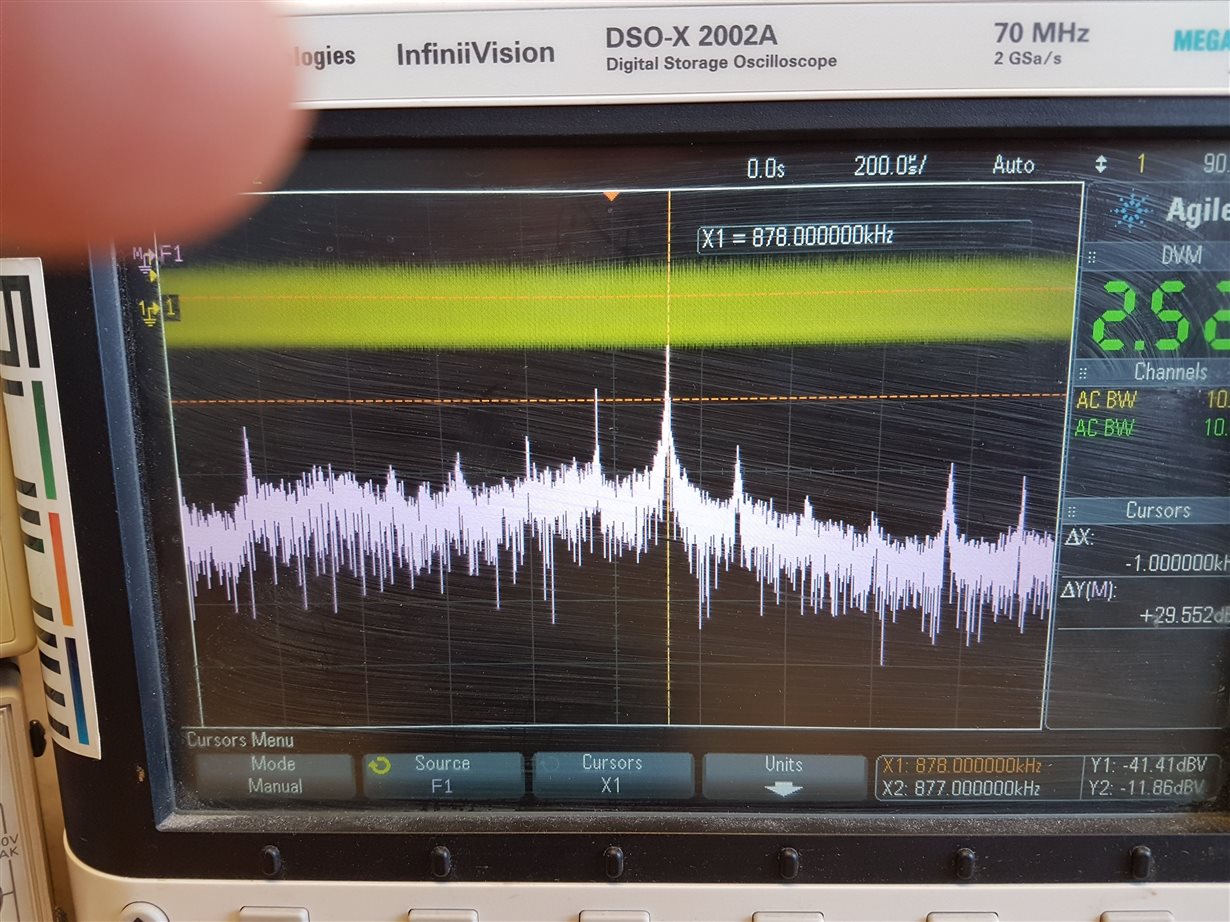

However, with certain devices, namely Macbooks from around 2012/2011 and iphone 4/4S, the speaker outputs a very loud hiss/noise when connected in AUX mode. I have analysed the output signal from the Macbook and iphone 4S and found a lot of noise between 100-500kHz in the order of 100mV or so all the time.

The codec input has a 10k + 470pF low pass filter on the input. However, this doesn't seem to be enough to stop the HF noise from getting through. Could this be anti-aliasing noise from the sigma-delta DAC on the Macbook/iphone which is coupling back into the audio band when sampled by the ADC in the 3254?

Is there anything I can do in software to improve or reduce this effect? The hardware is in production so difficult to add more filtering any time soon.

Looking forward to your reply.

David