There is a related thread which TI think ist solved, but we are wondering what the solution is?

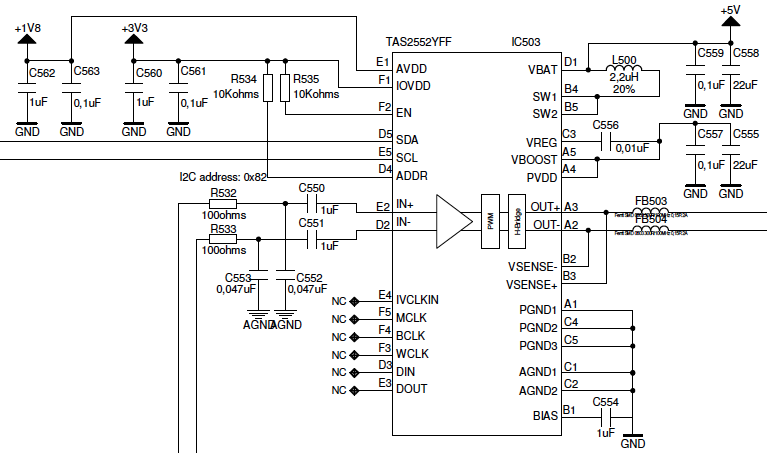

We are having a similar issue where we have boards with the TAS2552 which NAKs I2C requests.

We also had stronger pullups (1.2kohms) which we replaced by the 10k which the EVM uses, however, without any effect.