Other Parts Discussed in Thread: LM5010, ,

https://e2e.ti.com/support/audio/f/6/t/551486?tisearch=e2e-sitesearch&keymatch=TAS5756%20frequency

Referring to an old post.

This problem cropped up in my design as well. Chance is about 20% on every power cycle.

SPK_GAIN_FREQ actually glitches to 20dB/384kHz, volume output is noticably softer than normal condition.

All 6 boards exhibit the same problem.

Board only runs in BTL mode, so inductors used are TOKO, 1255AY-4R7M as per EVM. [edited: wrong p/n]

Board total idle current: 0.2A @ 24V @ 768kHz, output inductor temperature stable at ~60°C / IC package temp stable at 56~58°C.

Board total idle current during abnormal cycle: 0.39A @ 24V @ 384kHz, inductor temperature rises to 135°C+ IC temp rises up to 130+°C.

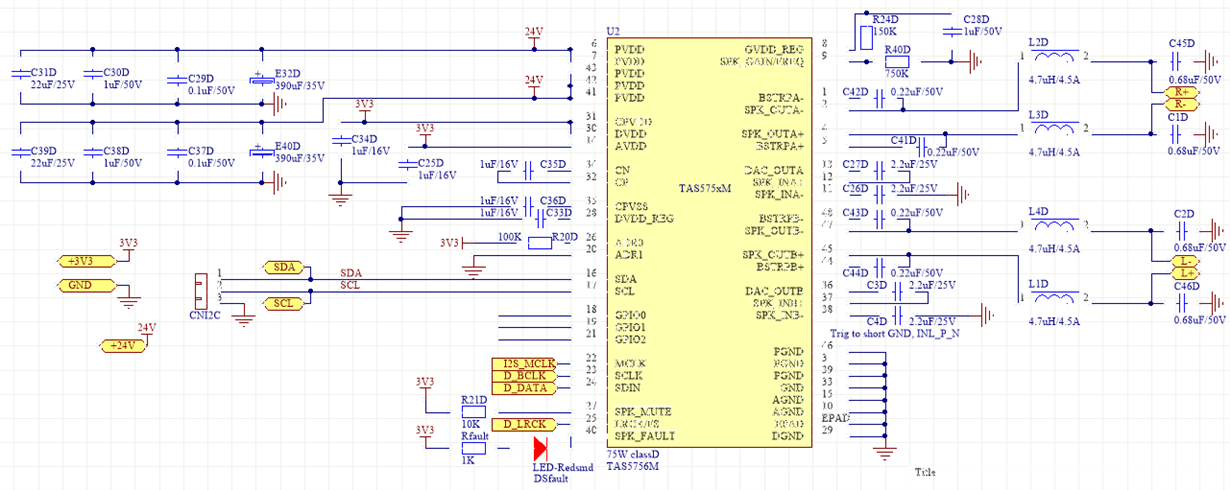

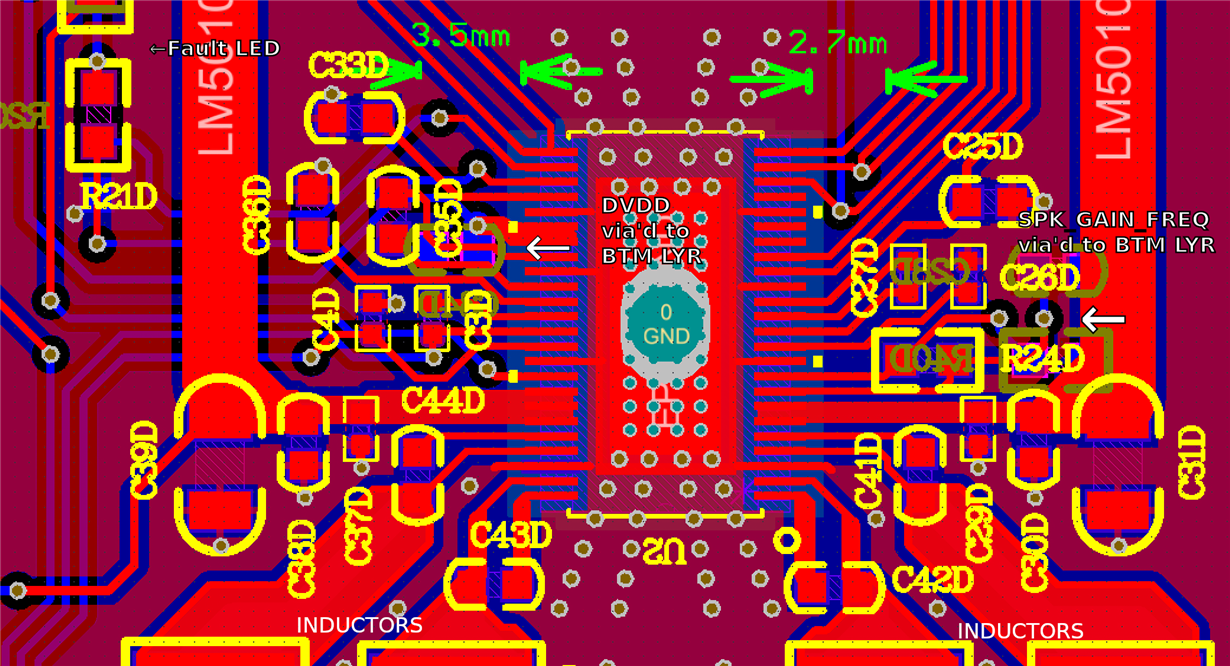

Schematic largely follows the EVM but with the addition of 390uF PBTL caps 1cm above the class D, in the PCB figure below.

SPK_GAIN_FREQ is set to 20dB/768kHz as per datasheet. SPK_GAIN_FREQ voltage is measured at ~5.7V. Scope shows an a smooth transition towards 5.7V without glitches.

I have desoldered and double checked all the capacitors used. All uF values are as per schematic.

I have tried adding a cap from 10nF up to 330nF to the SPK_GAIN_FREQ pin but it still triggers the abnormal condition. (Values above 330nF would trigger the TAS into 20dB/576 kHz with increased current)

I have tried resetting the I2S by means of holding I2S Master in reset and providing no MCLK; then re-apply MCLK and unassert I2S Master reset. There is still a chance to trigger abnormal condition.

I have tried the above (holding I2S Master in reset then unassert reset), but with MCLK always active, to no avail.

My 3V3 regulator was 29cm! away from the classD with 12mil/0.3mm trace width so, I have tried kludging a different 3v3 regulator just 3cm away from the ClassD. It does improve the 3v3 Vpk-pk and ripple waveforms, but the abnormal SPK_GAIN_FREQ still triggers.

I have tried adding pi filters to the 24V, 5V, and 3V3 to no avail. Added ferrites with same result.

I have tried adding 2x 20AWG wires for 24V/ground return from the classD and towards incoming power connector to no avail.

I have tried modifying the soft-start function on the LM5010 5V regulator to delay to ~300ms to allow the 24V to stablise no avail.

I have tried prolonging the voltage supervisor time to 1.1s (before enabling the I2S Master) to no avail.

Since the design daisy-chains the I2S devices; TAS I2S Slave to another I2S Slave; I have tried cutting the I2S traces to feed I2S only into the TAS5756M to no avail. Abnormal SPK_GAIN_FREQ still occurs.

All I2S lines are buffered. There is no distortion or glitching or intermittent pop during audio playback.

I have tried replacing the TOKO inductors with the PBTL 4.7uH/13A inductors [edit: Wurth 7443330470, Rdc=9.8mOhm] to no avail. Current is noticeably lowered but abnormal SPK_GAIN_FRQ still occurs.

I have tried muting the ClassD using SPK_MUTE during power up to no avail.

I have tried putting the GVDD_REG bypass cap to the top layer to no avail.

I have tried adding the extra pair of 22uF/35V as per BTL 2.0 configuration; still to no avail.

The Fault LED does not light up during abnormal condition.

PSU is using a lab supply. Also occurs with 24VDC 3A adaptor.

If I slow ramp to 24V with the lab supply from 0V to 24V over 2~3 seconds, the abnonrmal SPK_GAIN_FREQ would not happen.

As per old thread, lower voltage also triggers abnormal SPK_GAIN/FREQ condition.

Help.

PCB