Hi

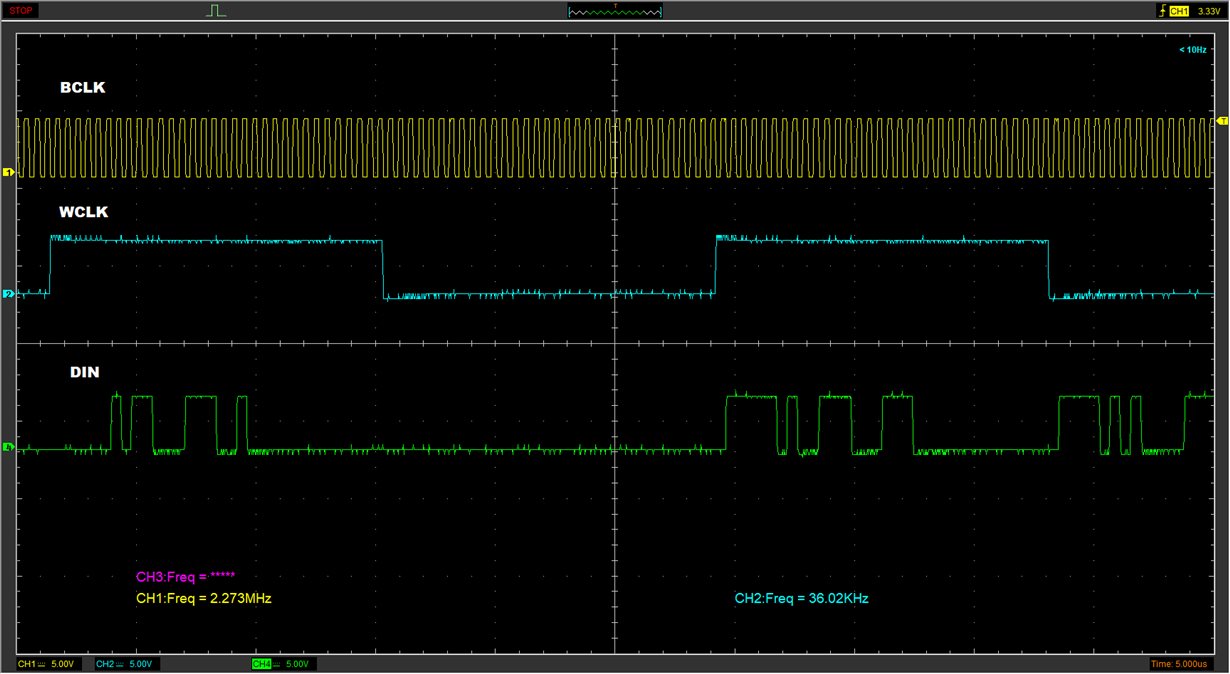

I am currently working to get sound from the ESP-WROVER-B to a 0.7W speaker using the TLV320DAC3120. I try to sent a 1 kHz tone to the speaker with the I2S protocol (sample rate: 36kHz, bit/sample 32). The result is a very noisy beep (see picture). I checked everything i could but cant find where the problem is coming from.

Here is the init for the codec:

Page, Register, Value

{0x00, 0x01, 0x01}, //reset

{0x00, 0x04, 0x07},

{0x00, 0x05, 0x91},

{0x00, 0x06, 0x08},

{0x00, 0x07, 0x00},

{0x00, 0x08, 0x00},

{0x00, 0x1B, 0x00}, //NB bits/word 30: 32bits/ 00: 16bits

{0x00, 0x1C, 0x02},

{0x00, 0x0B, 0x82},

{0x00, 0x0C, 0x88},

{0x00, 0x0D, 0x00},

{0x00, 0x0E, 0x80},

{0x00, 0x3C, 0x19}, //processing block

{0x00, 0x3D, 0x05},

{0x00, 0x25, 0x90},

{0x08, 0x01, 0x04},

{0x01, 0x1f, 0x1C},

{0x01, 0x2A, 0x04},

{0x01, 0x20, 0x86},

{0x01, 0x21, 0x4E},

{0x01, 0x23, 0x40},

{0x01, 0x24,0x80},

{0x01, 0x1f, 0x84},

{0x01, 0x28, 0x06},

{0x01, 0x26, 0x00}, // 0: Analog vol out not routed 80: Analog vol out routed to out class-D driver

{0x01, 0x2E, 0x0B},

{0x00, 0x3F, 0x96},

{0x00, 0x40, 0x04}, //unmute dac

{0x00, 0x41, 0x00}, //dac volume

Scoop of the I2S: