Hello everyone,

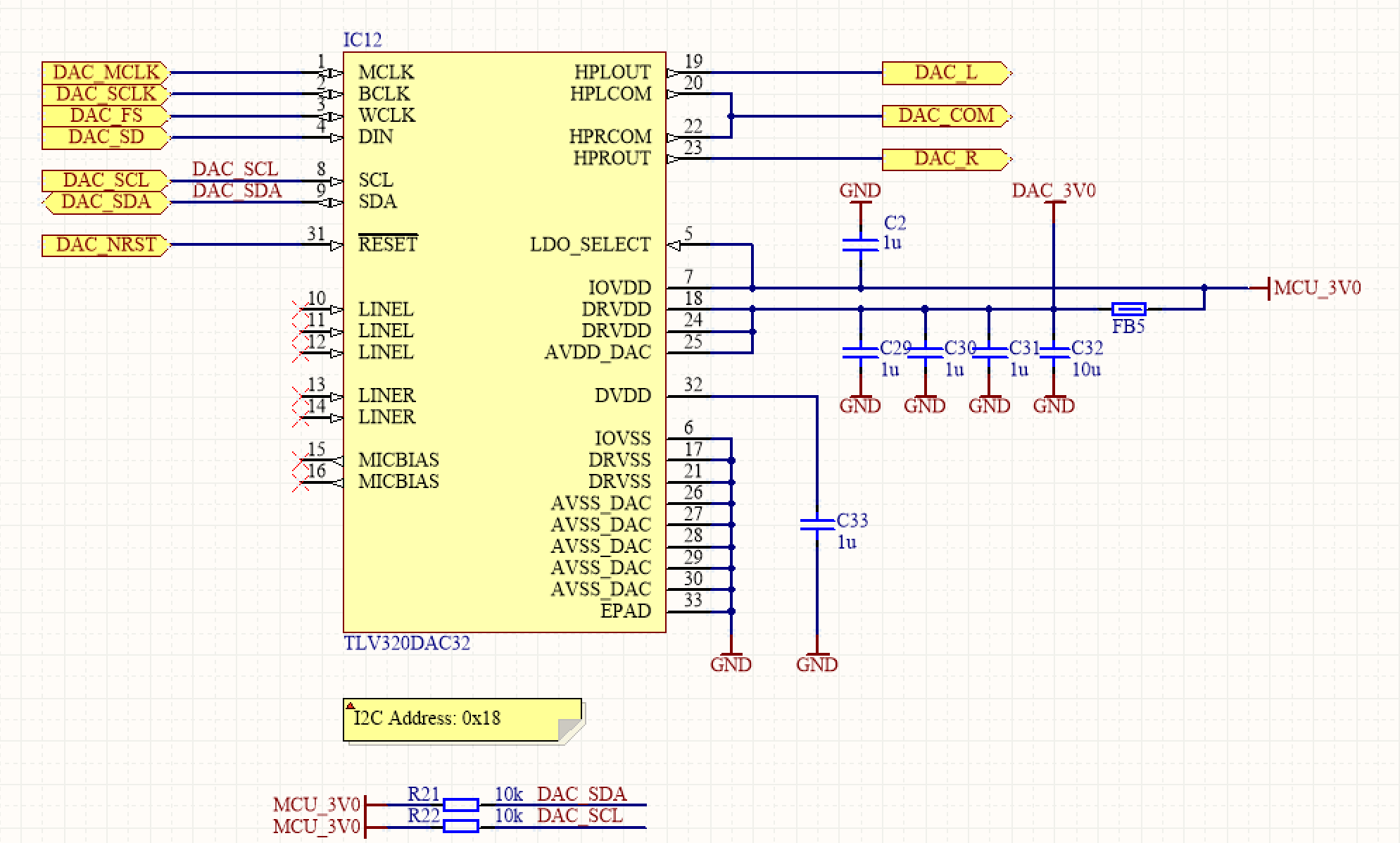

I am having a great deal of trouble when trying to put the TLV320DAC32 into power down mode in order to achieve lowest possible current consumption. In my system I've configured the TLV320DAC32 to use it's internal LDO since I don't have a 1.8V rail. The LDO_SELECT is driven from a microcontroller pin so that I can disable the LDO when the DAC is not used any longer (I don't know if that's a correct thing to do, but the LDO on it's own adds 2mA to overall current consumption). The 3.0V rail that I power the IOVDD DRVDD and AVDD_DAC is always at 3.0V as it is being used all over the system to power other things.

I've prepared the simplest possible firmware in order to observe the chip's behavior that basically does one job: toggles the reset pin at the start of the execution, while keeping the internal LDO off. This results in 6.5mA being consumed - far from calling it a low power state. Then what I did was to do the RESET toggling while keeping the LDO on and after a short period of time (10ms) bring the LDO to the off state. This in turn resulted in a negligible current consumption (few uA for the entire system) BUT after like a minute or so (of complete inactivity from the side of the MCU as it was put into deep sleep mode) the current rocketed back to 6.5mA!

All of the audio serial interface pins are driven low during the experiment, I2C pins (which were not used in this setup) were kept high by the external pull-ups.

Obviously I am not using the correct sequence to keep the DAC in the power down state, but then again I cannot find any sort of programming manual on the TI website that would describe the correct register programming sequence for bringing the DAC's power up and down. Would you be kind enough to explain to me what excactly should I do in order to achieve the power-down consumption as specified in the DAC's datasheet?

Kind Regards,

Tomek