Other Parts Discussed in Thread: PCM5122

Hello,

I've made another hardware spin that allows for software mode configuration of the PCM5242 and am looking to configure the chip to work with an input I2S stream based on 48kHz audio. The datasheet references a SLAC622, which doesn't seem to exist anymore (or maybe never did, if my search of the forums is correct).

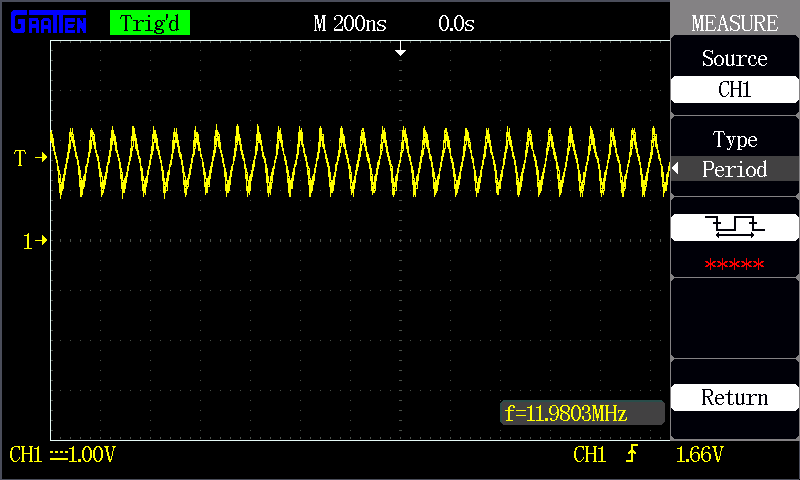

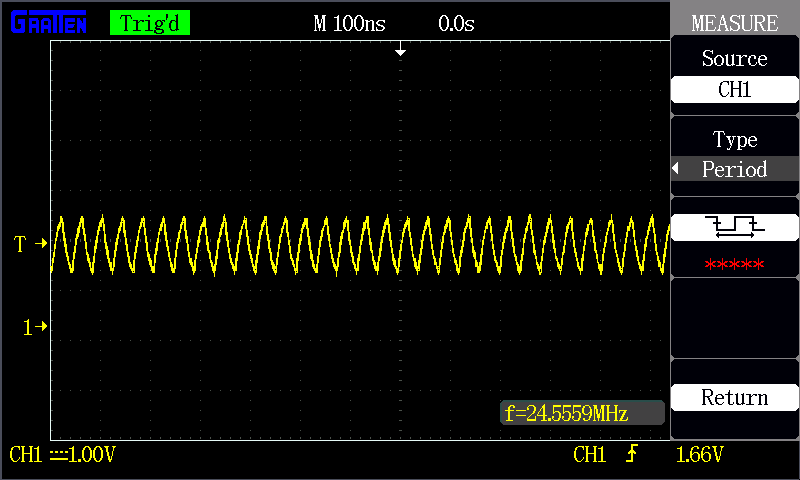

I've been following section 8.8.7 of the datasheet ("Clock Master from a Non-Audio Rate Master Clock"), and have configured the GPIO6 as the input to the PLL w/a 12MHz clock. The PLL is configured to be running at 98.304MHz (R = 1, J = 8, D = 1920, P = 1). I've configured GPIO5 to be an output of PLL/4, which is 24.576MHz. I've configured the DAC to use SCK as the reference clock.

Now I'm trying to understand what to do about BCK and LRCK; presumably these need to be aligned with the SCK (which is jumpered to GPIO5, so is running at 24.576MHz). Section 8.8.7 of the datasheet seems to mention these are outputs of the PCM5242. However, I am not understanding how that works, since my USB-to-I2S stage (CP2615) outputs the 4 I2S signals, so I'm not sure how to rectify this.

CP2615 | PCM5242

-> SCLK (bit clock) -> | o- BCK (Pin 27)

-> MCLK (12MHz) -> | o- GPIO6 -> PLL -> GPIO5 -> SCK (Pin 26)

-> DATA (data) -> | o- DIN (Pin 28)

-> LRCK (left/right) -> | o- LRCK (Pin 31)

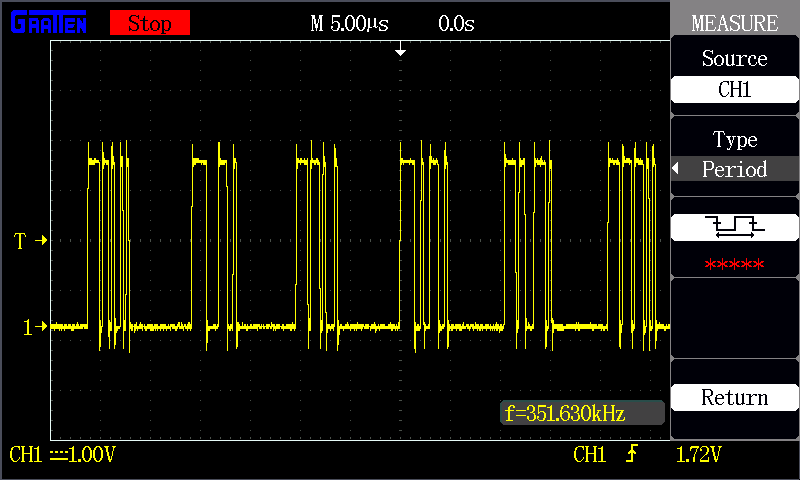

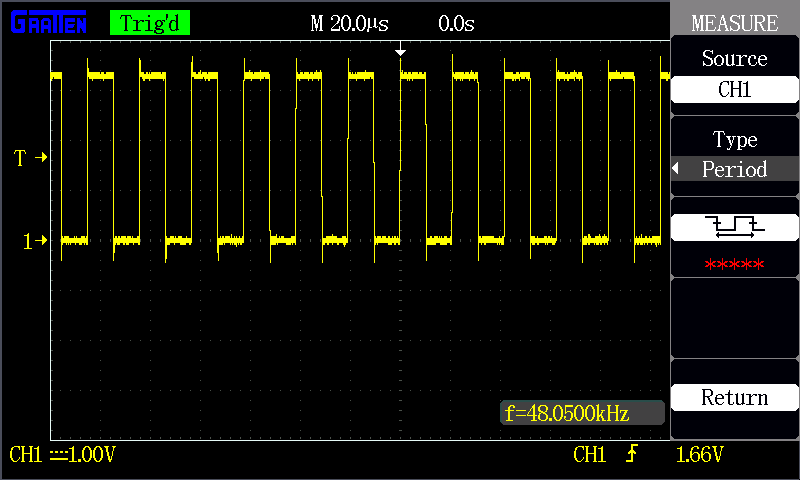

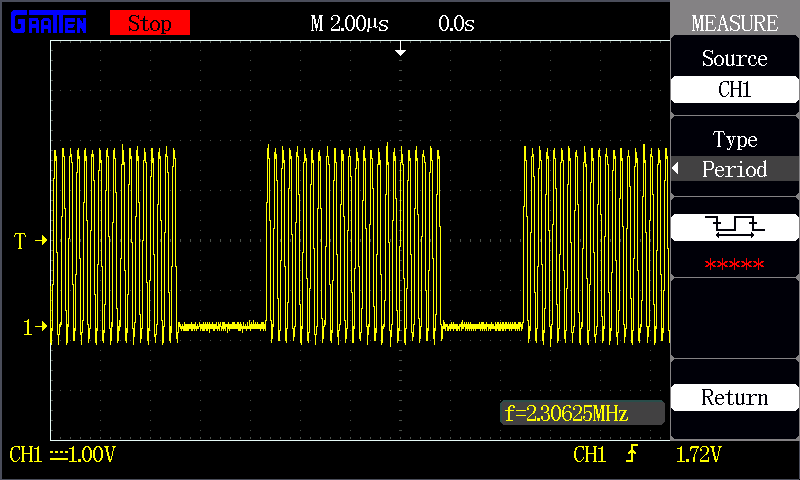

Any help you could provide would be appreciated! I've scoped out the signals and they appear to be what I expect (GPIO5 is outputting 24.576MHz). Just for kicks, I hooked up the BCK, DIN and LRCK signals, but register 91 reads 0x30, which indicates that the SCK is not a valid ratio of the sample clock.

Thank you