Hello,

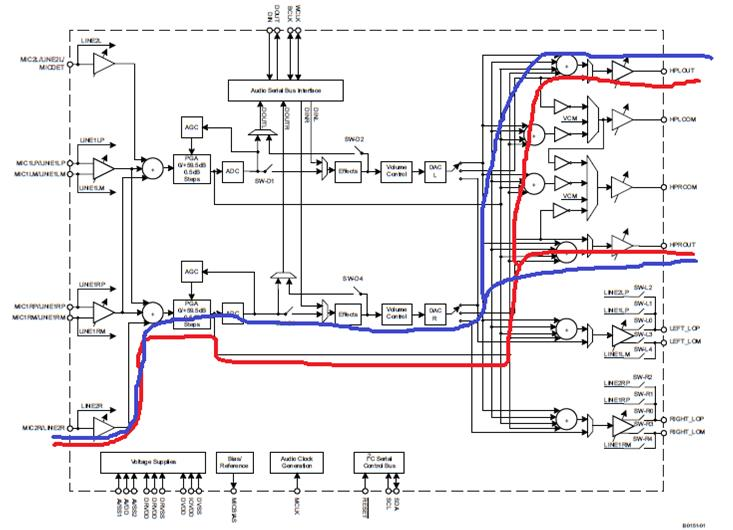

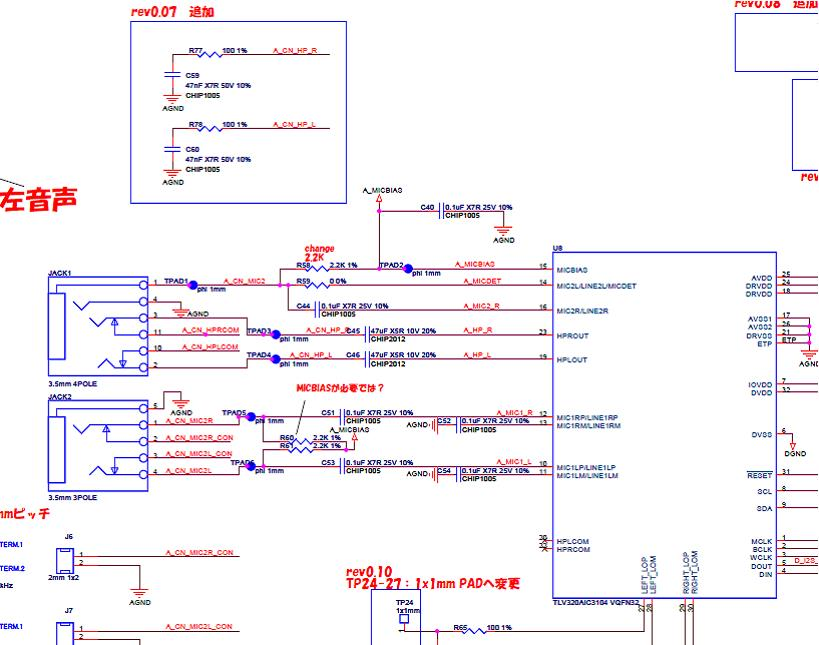

The customer wants to output sound from HPROUT/HPLOUT as same sound as MIC2R for debug purpose but they can't do this yet.

They would like TI to advise what register setting is mistaking.. Would you review the register setting? The path image is attached. Either red or blue line is ok for debug purpose.

The below is register dump information.

[ 0] = (0x00)

[ 1] = (0x00)

[ 2] = (0x00)

[ 3] = (0x10)

[ 4] = (0x04)

[ 5] = (0x00)

[ 6] = (0x00)

[ 7] = (0x0a)

[ 8] = (0x20)

[ 9] = (0x00)

[ 10] = (0x00)

[ 11] = (0x31)

[ 12] = (0x00)

[ 13] = (0x8b)

[ 14] = (0x80)

[ 15] = (0x00)

[ 16] = (0x00)

[ 17] = (0xf0)

[ 18] = (0xff)

[ 19] = (0x7f)

[ 20] = (0x78)

[ 21] = (0x78)

[ 22] = (0x7f)

[ 23] = (0x78)

[ 24] = (0x78)

[ 25] = (0x46)

[ 26] = (0x00)

[ 27] = (0xfe)

[ 28] = (0x00)

[ 29] = (0x00)

[ 30] = (0xfe)

[ 31] = (0x00)

[ 32] = (0x00)

[ 33] = (0x00)

[ 34] = (0x00)

[ 35] = (0x00)

[ 36] = (0xcc)

[ 37] = (0x20)

[ 38] = (0x06)

[ 39] = (0x00)

[ 40] = (0x02)

[ 41] = (0x00)

[ 42] = (0x00)

[ 43] = (0x00)

[ 44] = (0x00)

[ 45] = (0x00)

[ 46] = (0x80)

[ 47] = (0x00)

[ 48] = (0x00)

[ 49] = (0x00)

[ 50] = (0x00)

[ 51] = (0x0f)

[ 52] = (0x00)

[ 53] = (0x00)

[ 54] = (0x00)

[ 55] = (0x00)

[ 56] = (0x00)

[ 57] = (0x00)

[ 58] = (0x04)

[ 59] = (0x00)

[ 60] = (0x00)

[ 61] = (0x00)

[ 62] = (0x00)

[ 63] = (0x80)

[ 64] = (0x00)

[ 65] = (0x0f)

[ 66] = (0x00)

[ 67] = (0x00)

[ 68] = (0x00)

[ 69] = (0x00)

[ 70] = (0x00)

[ 71] = (0x00)

[ 72] = (0x06)

[ 73] = (0x00)

[ 74] = (0x00)

[ 75] = (0x00)

[ 76] = (0x00)

[ 77] = (0x00)

[ 78] = (0x00)

[ 79] = (0x00)

[ 80] = (0x00)

[ 81] = (0x00)

[ 82] = (0x00)

[ 83] = (0x00)

[ 84] = (0x00)

[ 85] = (0x00)

[ 86] = (0x00)

[ 87] = (0x00)

[ 88] = (0x00)

[ 89] = (0x00)

[ 90] = (0x00)

[ 91] = (0x00)

[ 92] = (0x00)

[ 93] = (0x00)

[ 94] = (0x06)

[ 95] = (0xc4)

[ 96] = (0xc4)

[ 97] = (0xc4)

[ 98] = (0x00)

[ 99] = (0x00)

[100] = (0x00)

[101] = (0x01)

[102] = (0x02)

[103] = (0x00)

[104] = (0x00)

[105] = (0x00)

[106] = (0x00)

[107] = (0x00)

[108] = (0x00)

[109] = (0x00)

[110] = (0x00)

[111] = (0x00)

[112] = (0x00)

[113] = (0x00)

[114] = (0x00)

[115] = (0x00)

[116] = (0x00)

[117] = (0x00)

[118] = (0x00)

[119] = (0x00)

[120] = (0x00)

[121] = (0x00)

[122] = (0x00)

[123] = (0x00)

[124] = (0x00)

[125] = (0x00)

[126] = (0x00)

Best regards,

Toshihiro Watanabe