Hi Team,

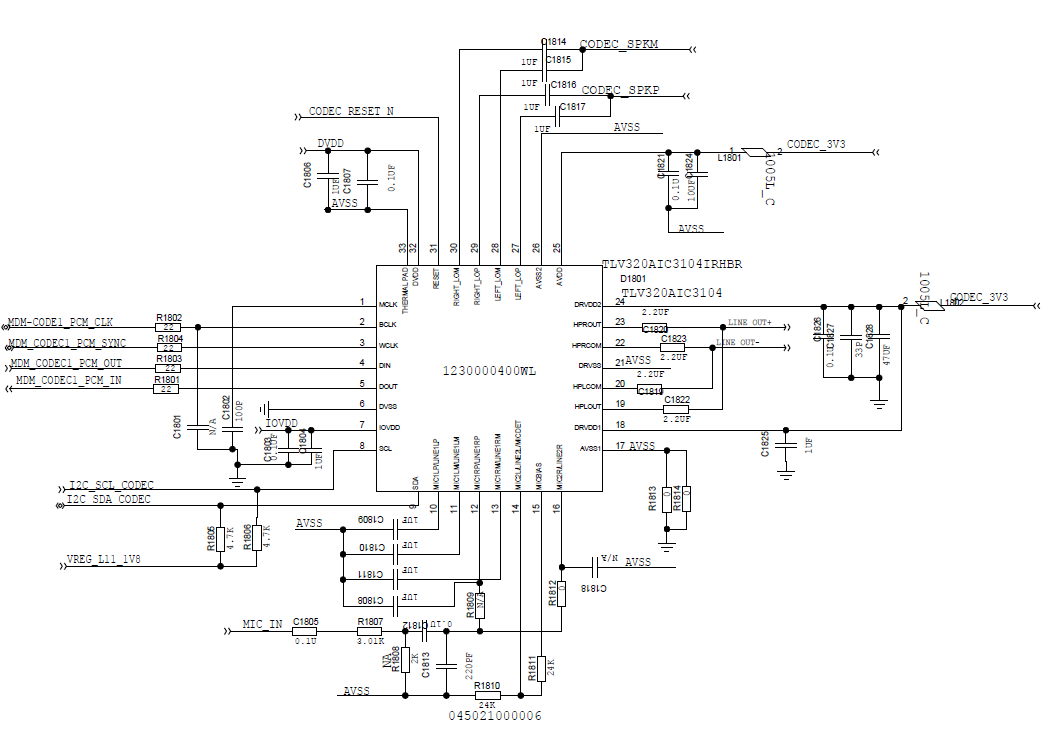

Our customer found big output noise issue when using AIC3104. Its application scenario is Modem with DSP + codec through I2C/I2S/RESET/GND.

Please refer to the below schematic. We have removed C1819/C1820/C1822/C1823/C1815/C1817. Following codec CODEC_SPKP/M is TPA3111. We have measured the noise is from codec side, not TPA3111.

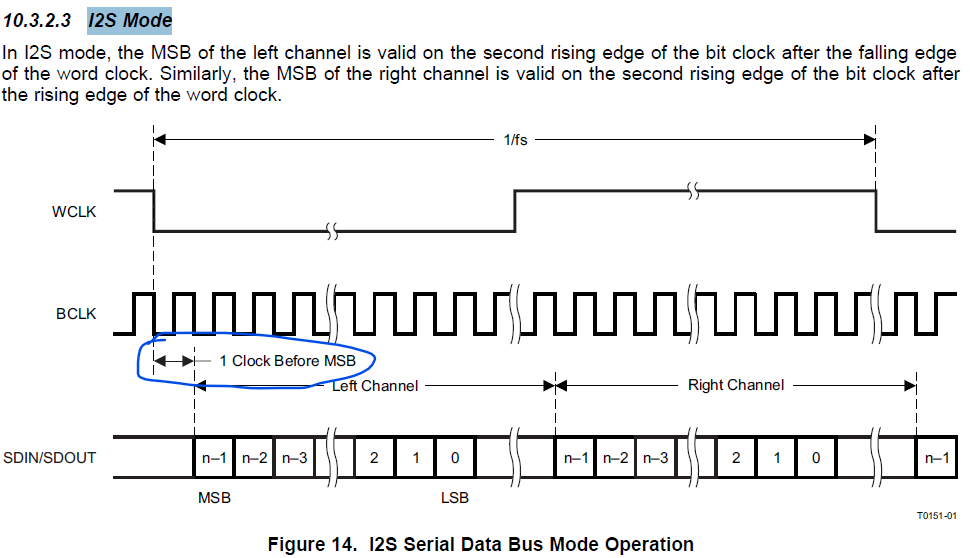

(BCLK=1.536MHz, WCLK=48kHz)

We have tried several tests:

1) Let our customer record the music before sending to codec. The record voice is ok and there is no noise. That is to say, the input source has no noise.

2) Try different audio sources, such as Silence, LR music and silent_dtmf5. When we play silence, it has no noise. When we play music, it has noise.

We download the related registers and the value is in the below. For different audio sources, the register value is the same.

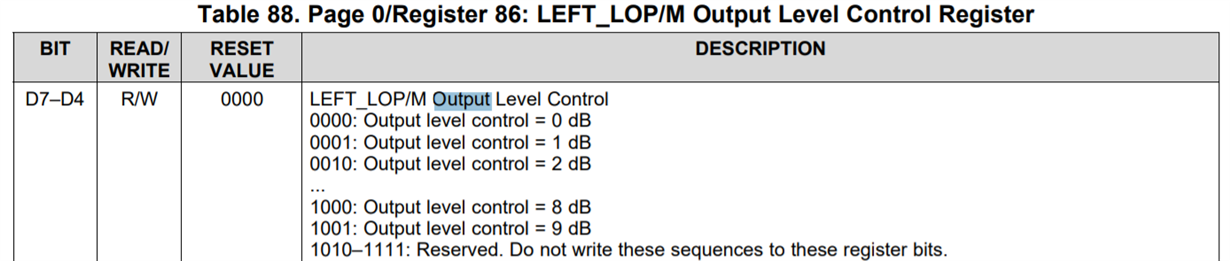

3) Try to change the left output and right output volume. The noise level doesn't change.

Need your help:

1) Do you have any more suggestions to find out the root cause of big output noise issue?

2) Why there is no output noise when only playing silence? Even when playing "silent_dtmf5", it has discontinuous silence, the noise is still there.

3) Can you explain why I2S mode need addition clock before MSB? Is it to say, for the BCLK=1.536MHz, WCLK=48kHz, it can't support word length=32bit, correct?

The schematic is attached: