Part Number: SRC4392

Other Parts Discussed in Thread: PCM5142

Hi,

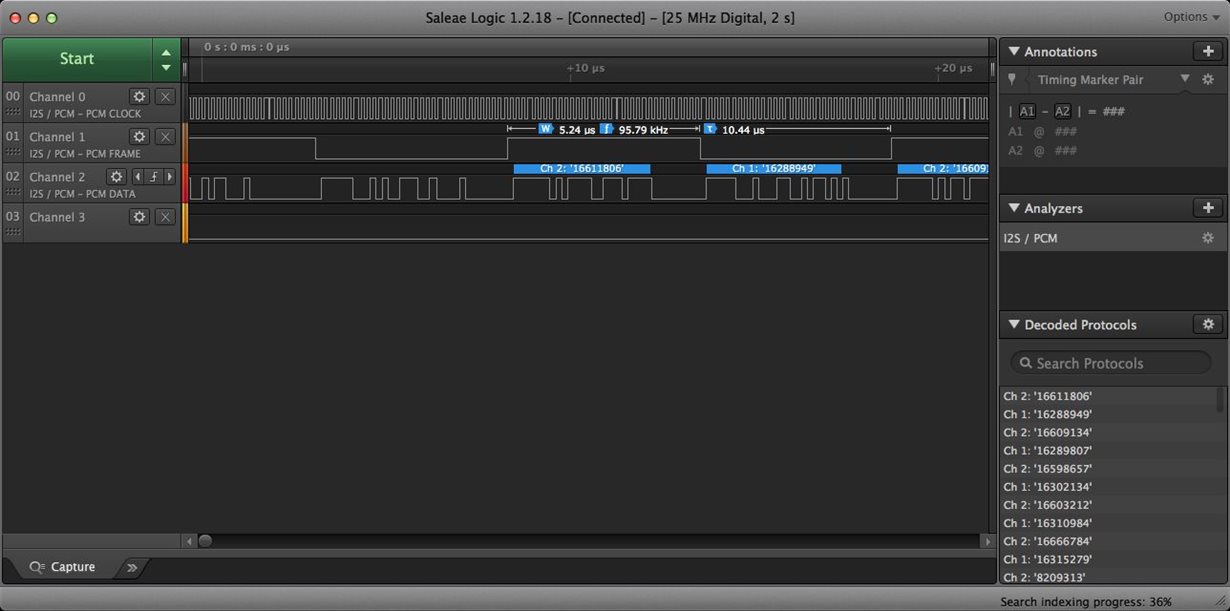

I have an almost-working prototype using an SRC4392 feeding a PCM5142, but I have one last problem: 16-bit data files won't play.

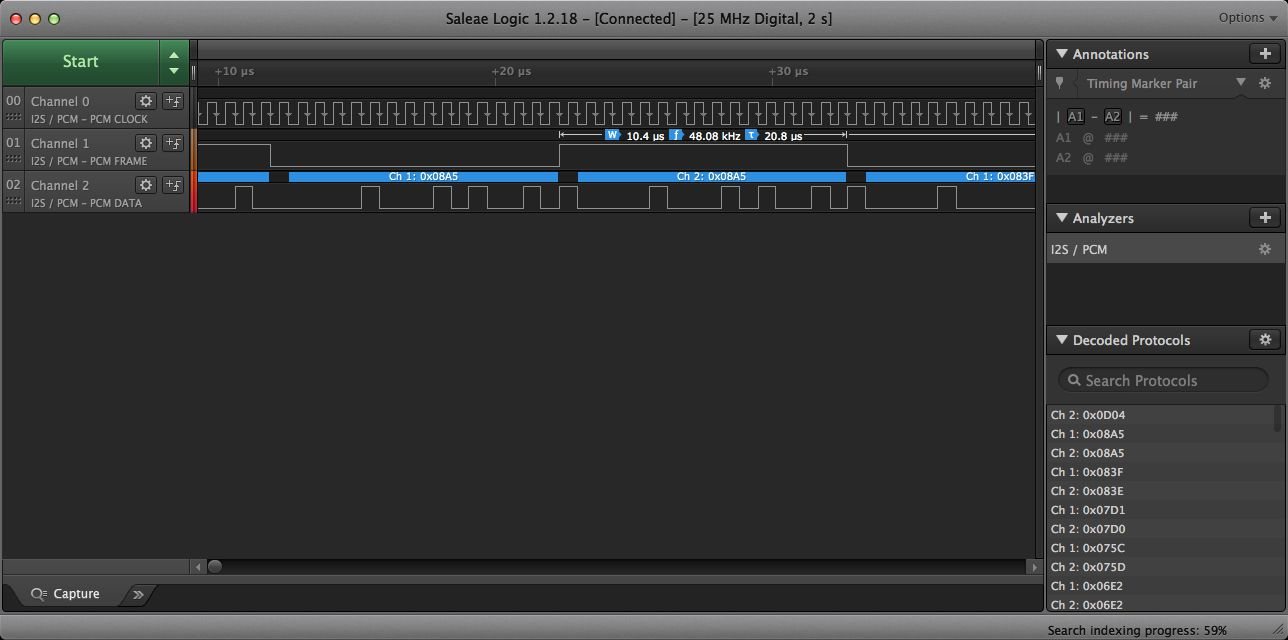

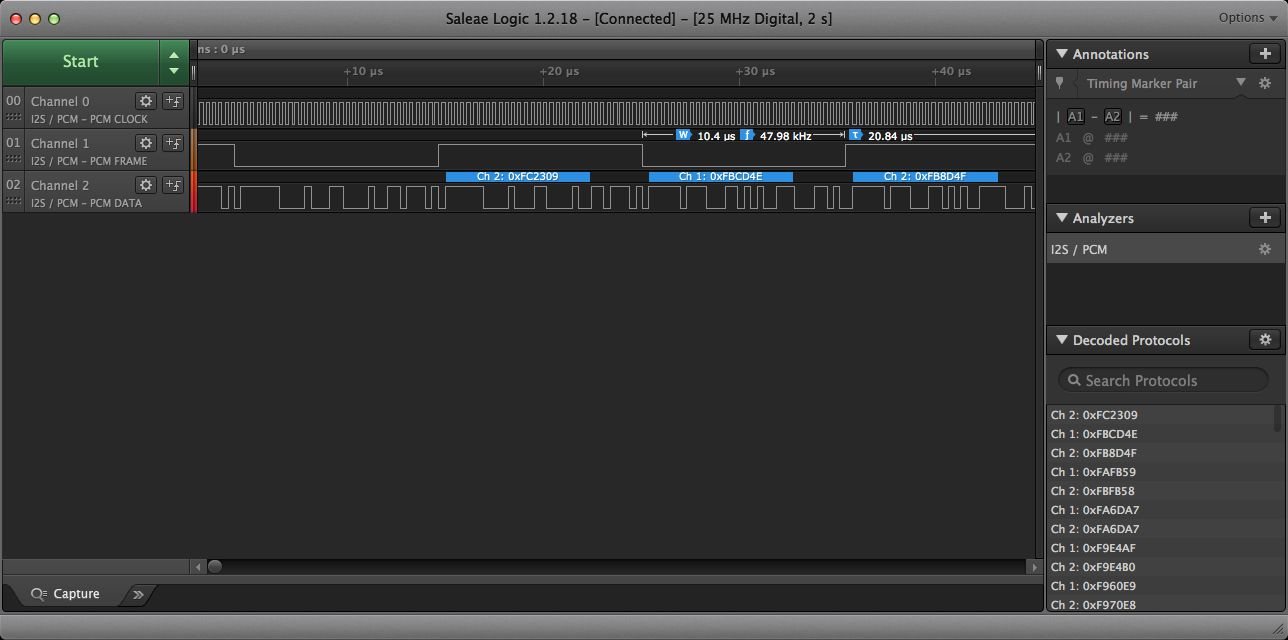

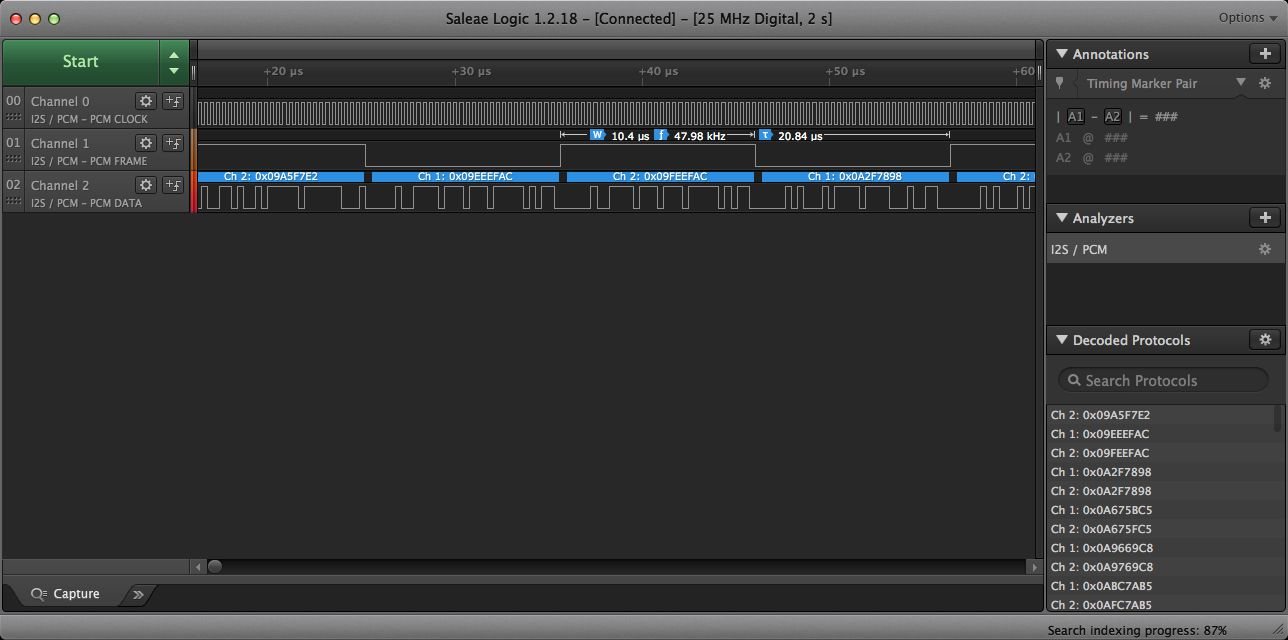

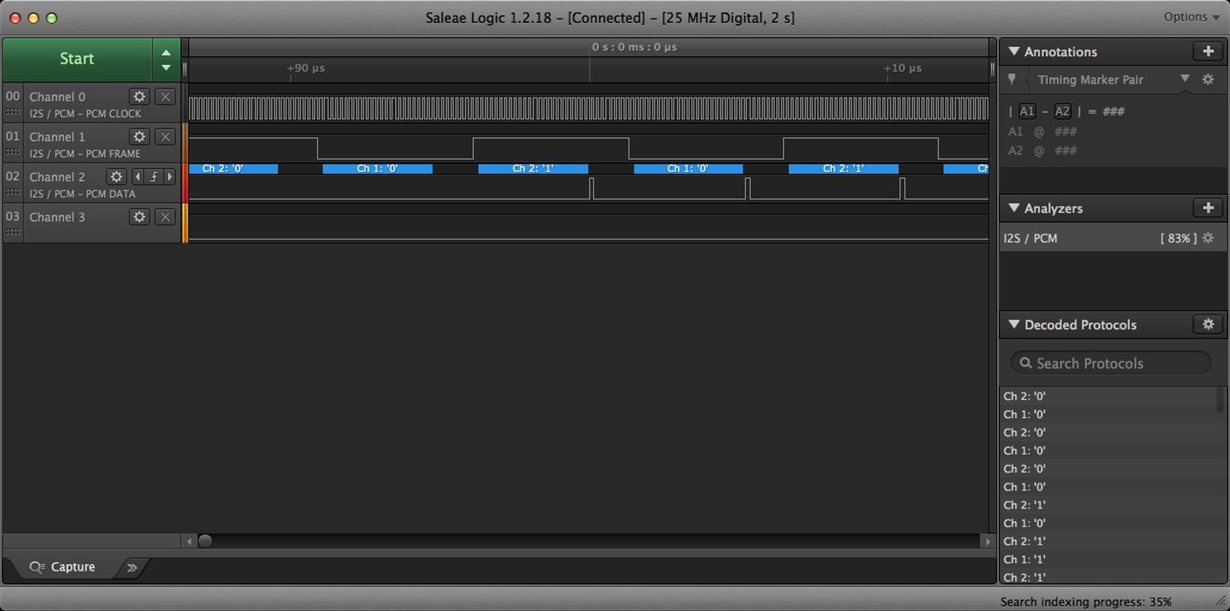

I'm feeding I2S audio into Port B set up as a slave, with the Port B data format set to 24-bit I2S.

Data from Port B goes through the SRC and is sent out Port A to the PCM 5142.

Port A is set up as a master and sends 24-bit I2S at 192kHz.

Port A and the SRC are driven by a 24.576MHz MCLK .

The PCM5142 receives 3-wire I2S (no SCK) so it is in slave mode.

Playing 24-bit and 32-bit files at 44.1kHz, 48kHz, 96kHz or 192kHz works fine. 16-bit files at 44.1kHz or 48kHz result in silence.

The RDY pin is pulled low for all files (inc. 16-bit) so it appears that Port B is receiving and the SRC is locking on to the clock for 16-bit files, but no output from Port A.

The 0x32 and 0x33 registers show the correct ratio for all of the files, including 16-bit.

Is this a supported use case? In other words, should the SRC4392 be able to output 24-bit 192kHz I2S data from 16-bit I2S input data? The I2S spec says that the received should complete or truncate incoming data to match its internal work length.

Thanks in advance,

Peter