Hello Professional,

I have question for PCM9211.

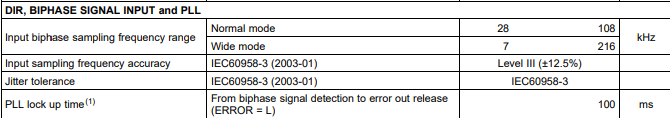

I'd like to know about the trigger of PLL unlock error. For example, I think No input signal, No preamble of input signal will cause Unlock error.

Is there the other trigger of causing Unlock error?

Best regards,

Kazuki Kuramochi