Hello Team,

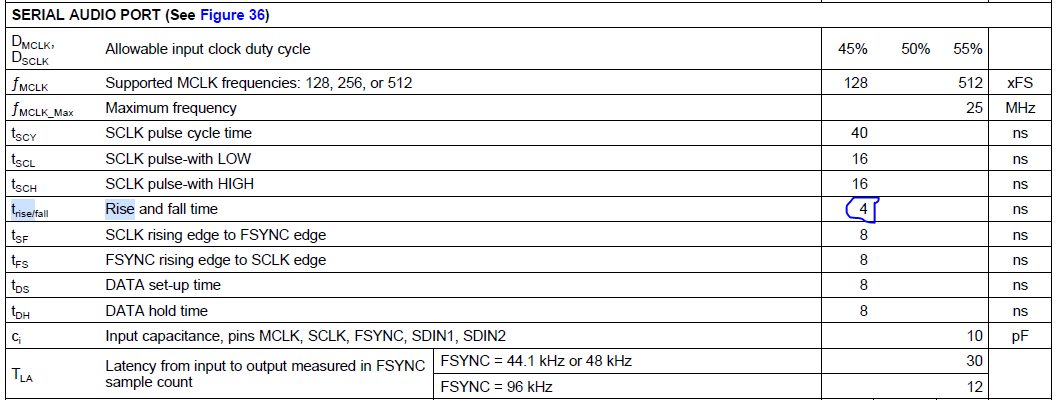

we need clarification regarding rise and fall time of FSYNC and DATA. Is the value in our datasheet also valid for FSYNC and DATA? Or only for BCLK.

My customer is using MCLK with 256xFS (12.288MHz). Currently they stretch this maximum value of 4ns at FSYNC to 4.5ns. Is this still acceptable? Because this would help to improve EMI issues.

Many Thanks

Josef