Other Parts Discussed in Thread: PCM3168

Hello all,

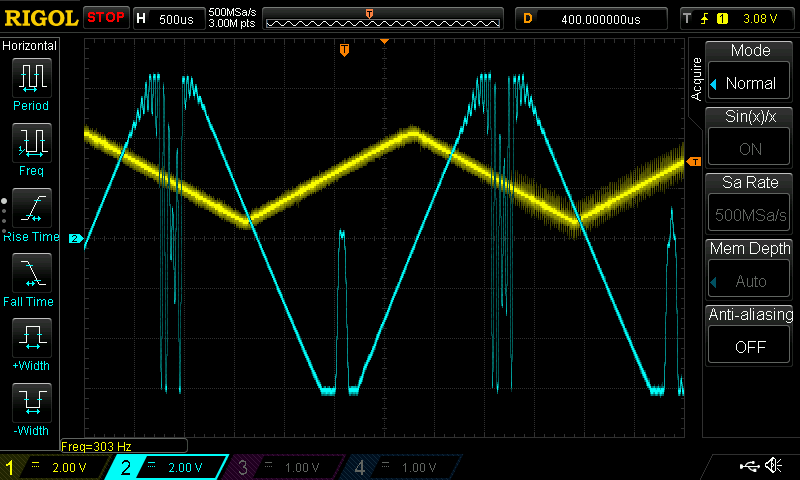

When driving the PCM3168 ADC inputs with an out of range value, I expect it to saturate at the extreme values. Specifically, if I overdrive the input I expect to see values that span from 0x800000100 to 0x7FFFFF00. Instead, on the high side I see an occasional glitch like the following. The input source is a triangle wave. Line 65 should be another 0x7FFFFF00 but it's not. Sometimes when going above the top of the range, one or more values will be random instead of full scale.

What am I missing? Background information below.

I'm using single sampling mode at 48kHz. Format: TDM 24 bit left justified.

I've tried switching the input HPF on and off. I've tried inverting the phase. I've tried attenuating the ADC signal. I'm getting good results when I keep the signal in bounds, but glitching when exceeding the range on the upper end. Yes, it would be possible to clamp the signal in the analog domain. I accustomed to one of your competitor's parts that handles this circumstance gracefully.

Thank you for your help.

Aaron Higgins