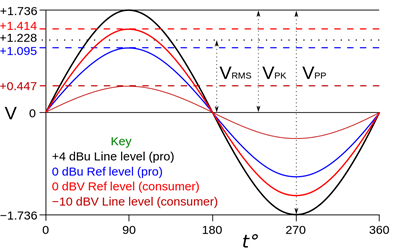

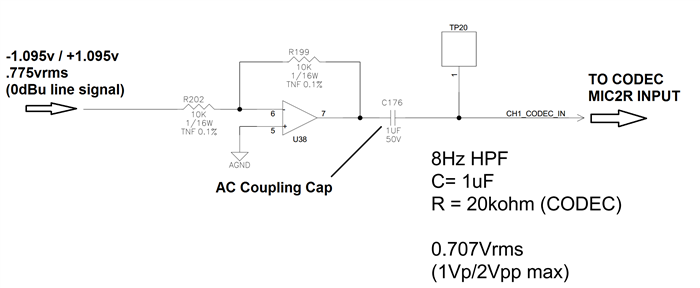

Per the datasheet, it indicates that the recommended level of inputs for these interfaces is 0.707Vrms. However the absolute min indicates -0.3v and the absolute max is AVDD+0.3v. We plan to inject a normal 0 dBu (pro audio signal) 0.775Vrms (-1.095v to +1.095v) line level signal, but this appears to be outside of the negative voltage range. However, when probing the input pin of the codec with DC coupling mode the codec appears to apply a DC offset to bring the signal up to around 0v to 2.19v. This would lead me to believe that the we are within the correct range.

Do these inputs apply the DC offset as a constant level or does it change based on the input signal?

Can you confirm this is using the codec correctly?

What are the maximum voltage ranges that can be applied to these interfaces?

Thanks!