Other Parts Discussed in Thread: PCM1803A,

Hi,

Are there any concerns if replacing PCM1803A with PCM1802?

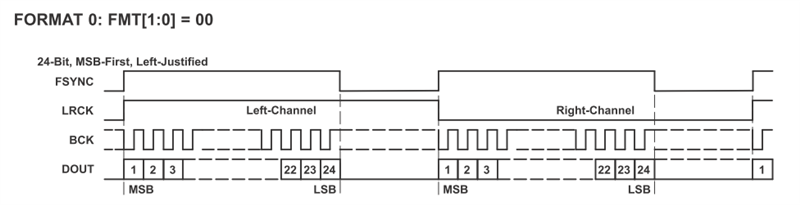

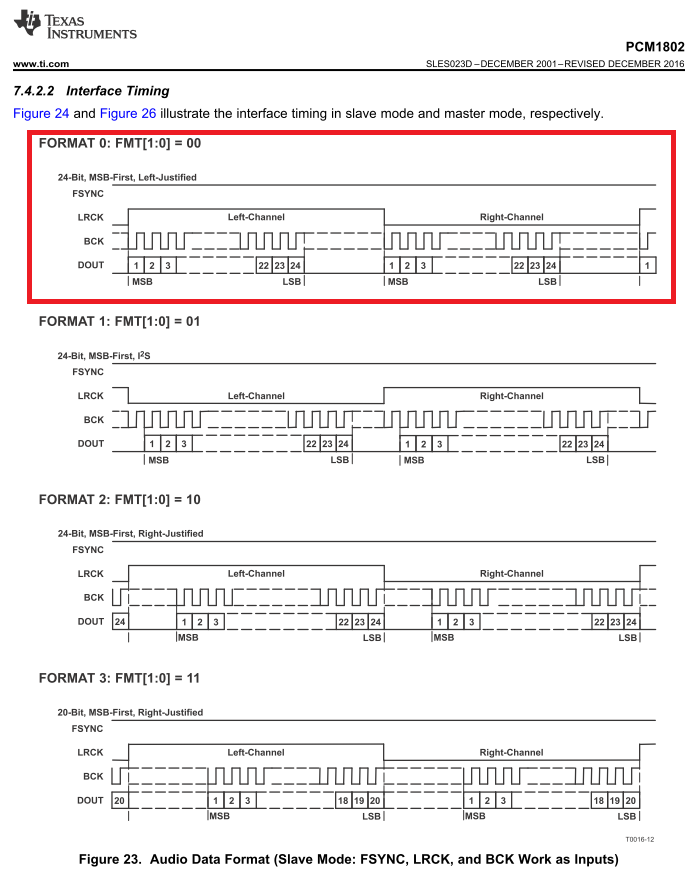

Is my understanding correct that FSYNC pin should be pulled-up to VDD with the slave mode(FMT1=0, FMT0=0, MODE1=0 and MODE0=0) for PCM1802?

Best regards,

Kato