Other Parts Discussed in Thread: PCM1840, TLV320ADC6140, TLV320ADC3140

Hello,

Our customer has got PCM1840EVM to confirm 4ch TDM master mode function.

There is strange behavior, at 44.1KHz TDM master mode is worked fine, all clocks and data were outputted at MSZ=H, FMT1=L, FMT0=L,MD0=L, MD1=MCLK 11.2896MHz

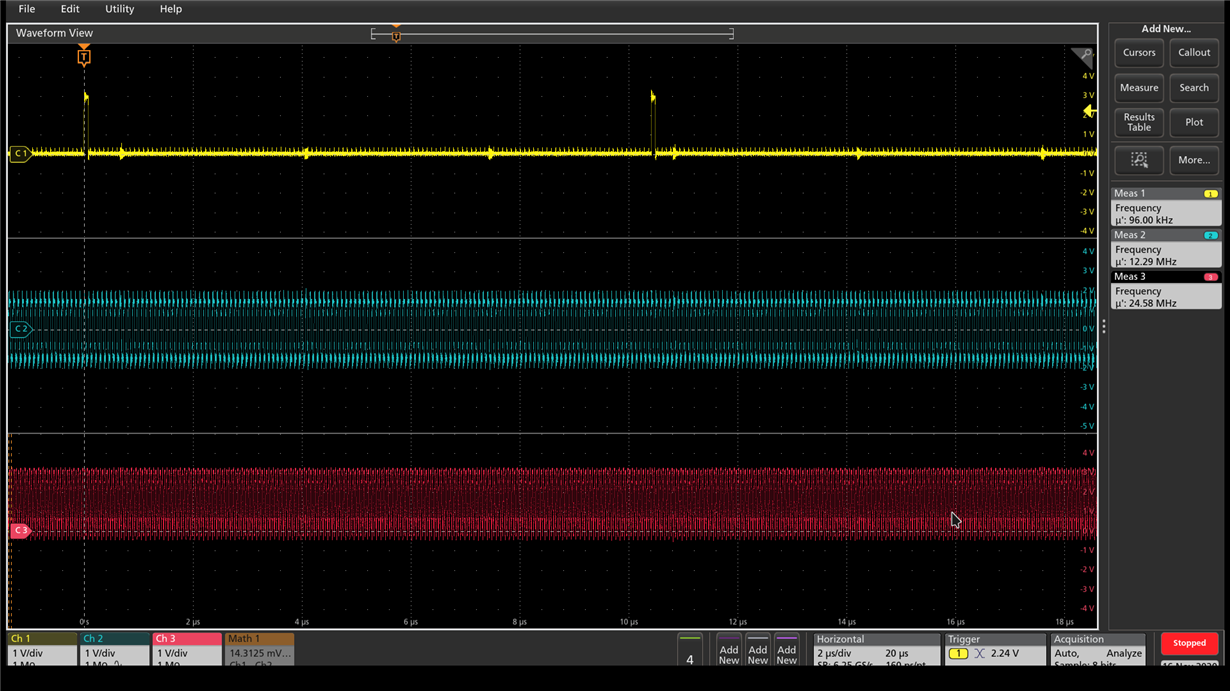

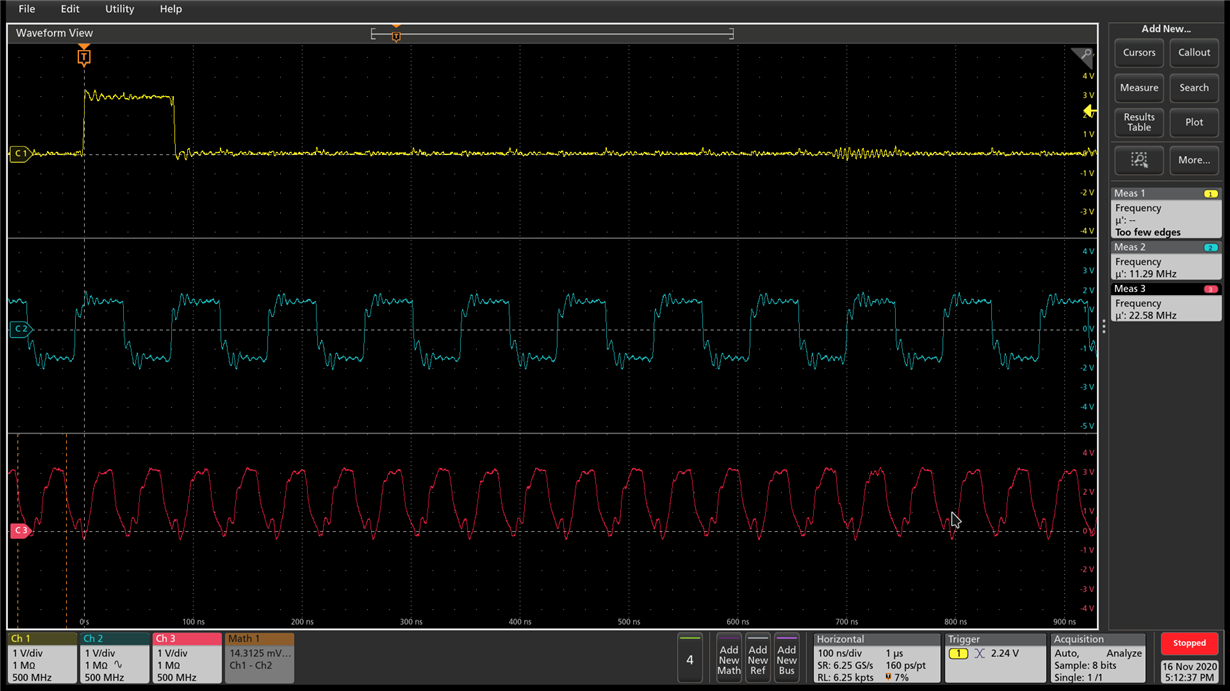

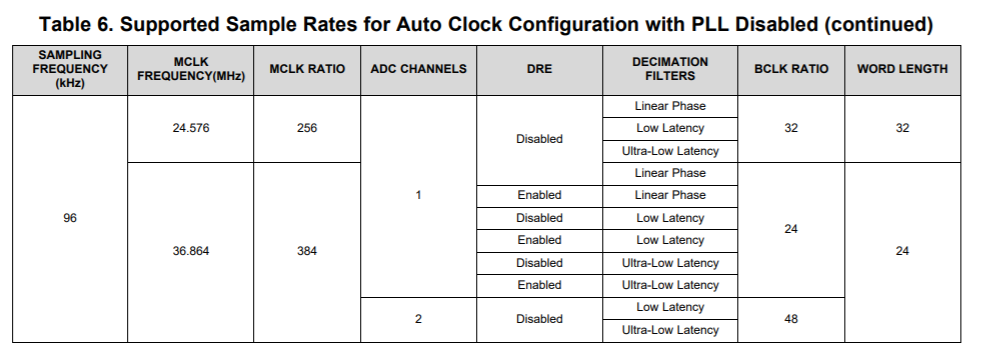

Then change MCLK to 24.576MHz as 256fs of 96KHz TDM master mode, we got right timing FSYNC/BCLK output clocks as attached capture image, but SDOUT is always 0.

Fs 88.2KHz is same situation.

Should we set decimation filter order by manually to PCM1840?

Or some kind of setting is required on the EVM?

Our customer need to release PCB layout quickly to replace a ADC from AKM.

Regards,

Mochizuki