Hi Expert,

I checked below post and still have some questions regarding the effect of the power up/down sequence.

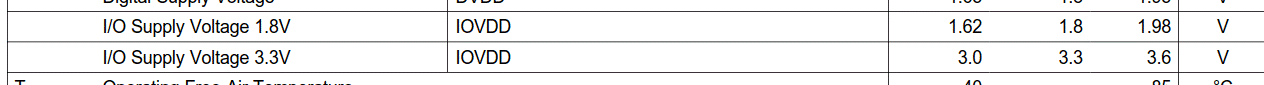

1. would you please explain more what does "faults at internal level shifters and/or diodes being forward biased" mean?

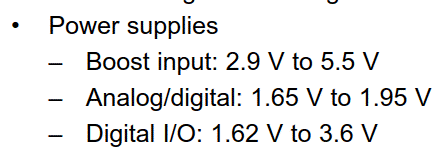

2. about IOVDD, is this a range we can use 1.62-3.6V or it has to be either 1.8V or 3.3V?

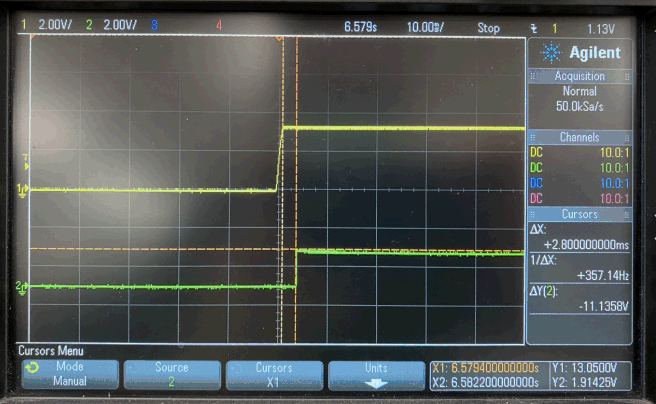

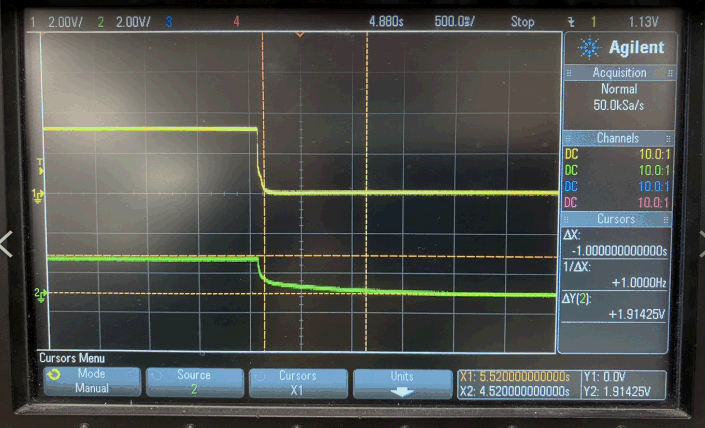

3. "the supplies should at least power down at the same time", the "same time" here means AVDD, DVDD=1.65 and IOVDD=1.62V? For IOVDD using 3.3V, the power down timing is still considered 1.62V or 3V?

4. does our EVM also follow the sequence? Since we couldn't tell it make the sequence design on the circuit.

Thank you.

Allan