hi Team :

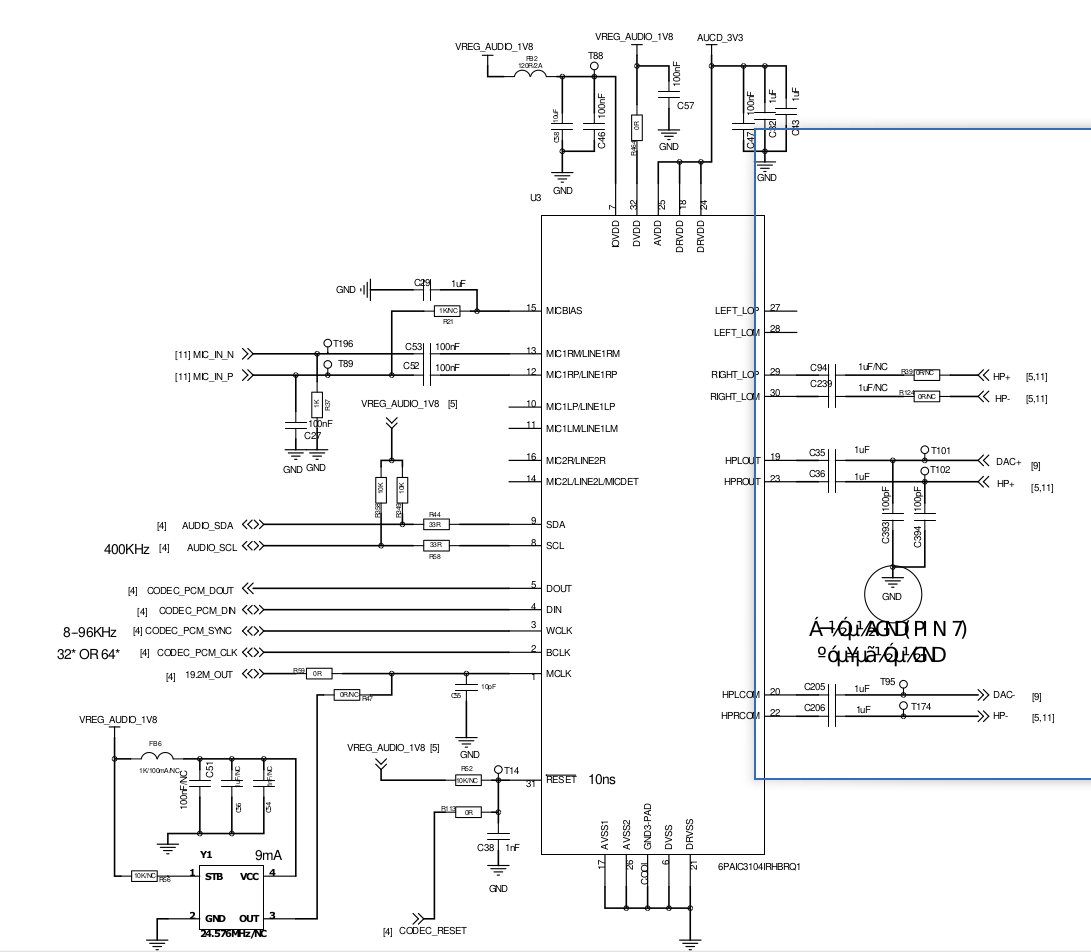

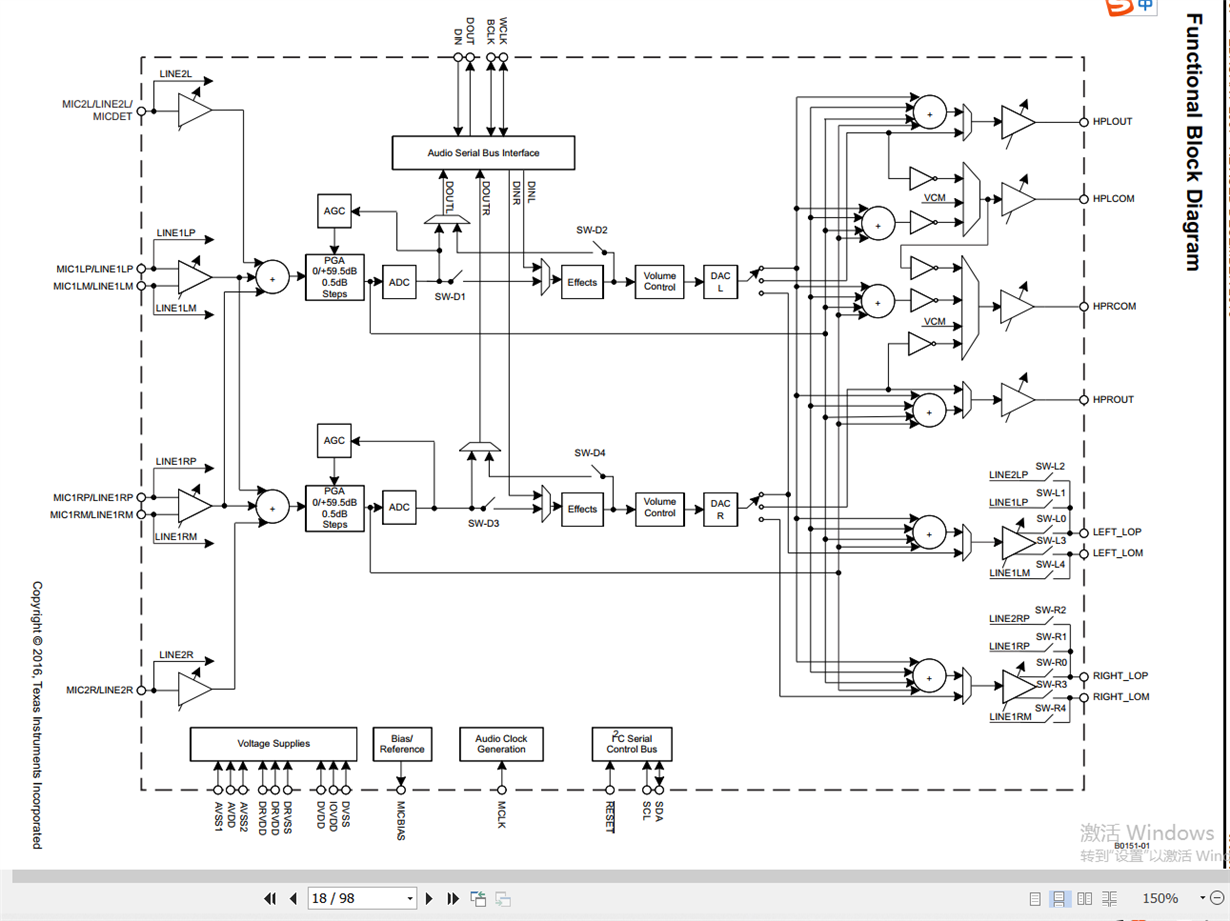

1 codec chips: TLV320AIC3104

1.1 kernel version : 3.18.48

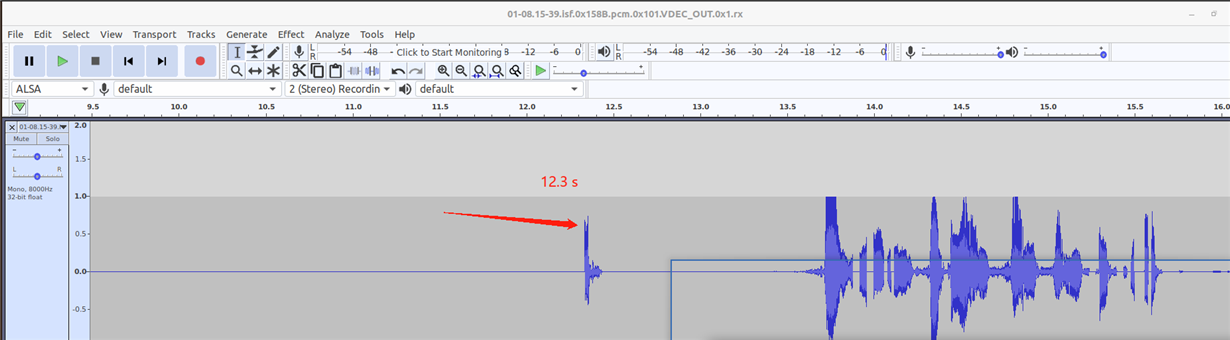

1.2 questions in short : heard a pop noise when we make a phone call .

1.3 questions in details :

1.3.1 the trouble is if we mute too early ,the head words of this phone call will be lost . Mute too late,the pop noise has been heard.

1.3.2 in addition, that noise didn't caused by channel switch .The output channel are opened since reset(power on ).

1.3.3 it's not a certain delta Time between call out and connected in .so that's hard to thinking in Linear time invariant ways.