Hi All,

I have a question about TAS5760M.

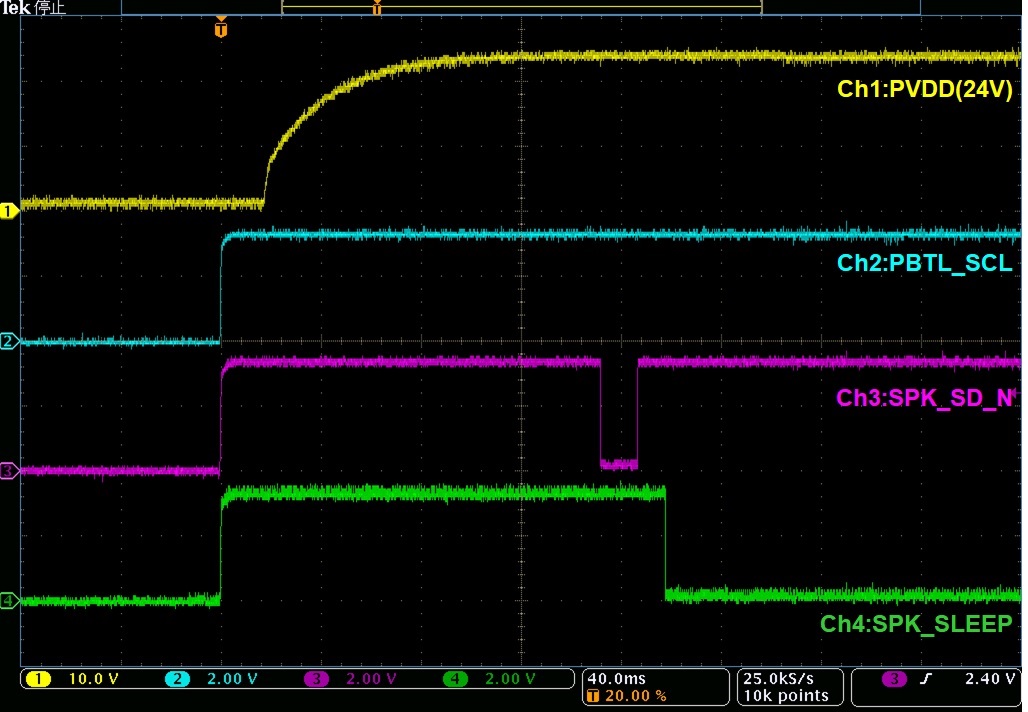

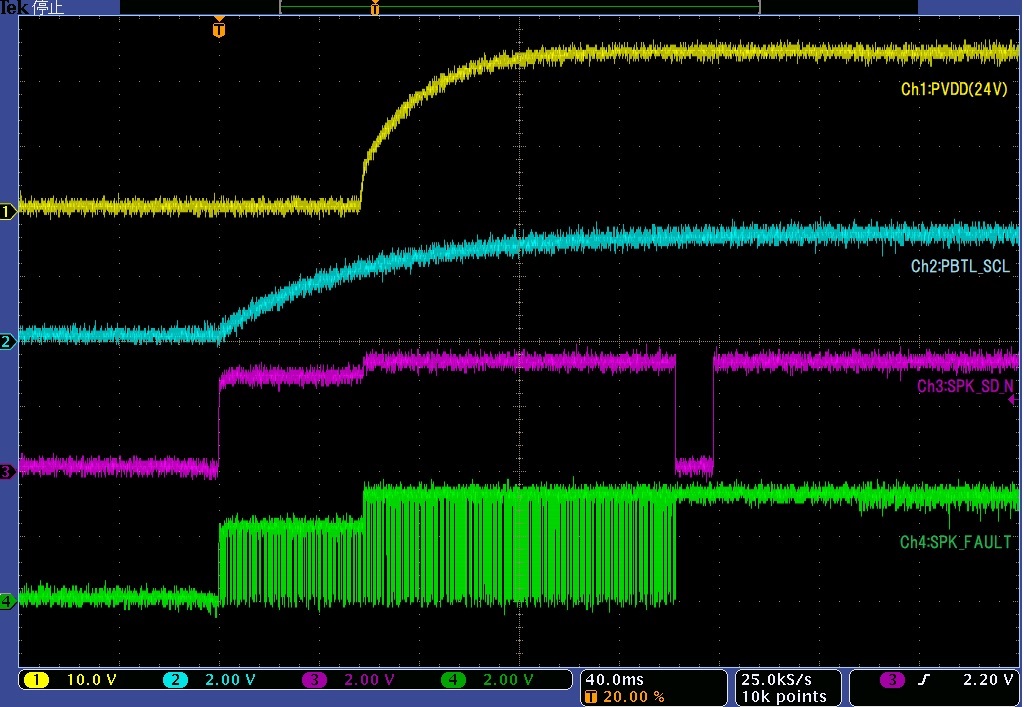

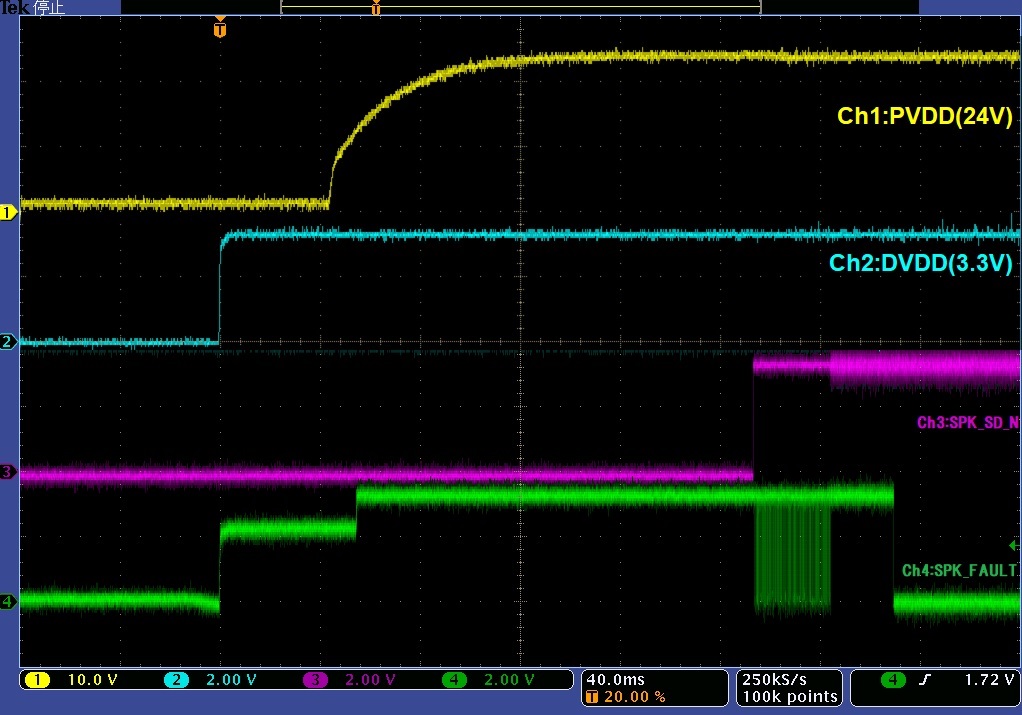

In rare cases, the SPK_FAULT signal is asserted low when the power is turned on at low temperatures.

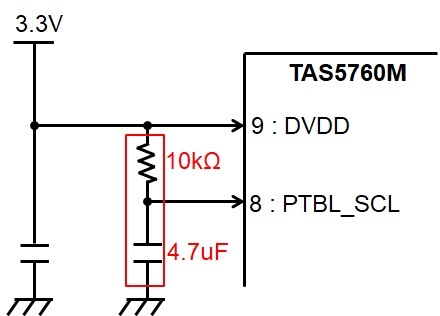

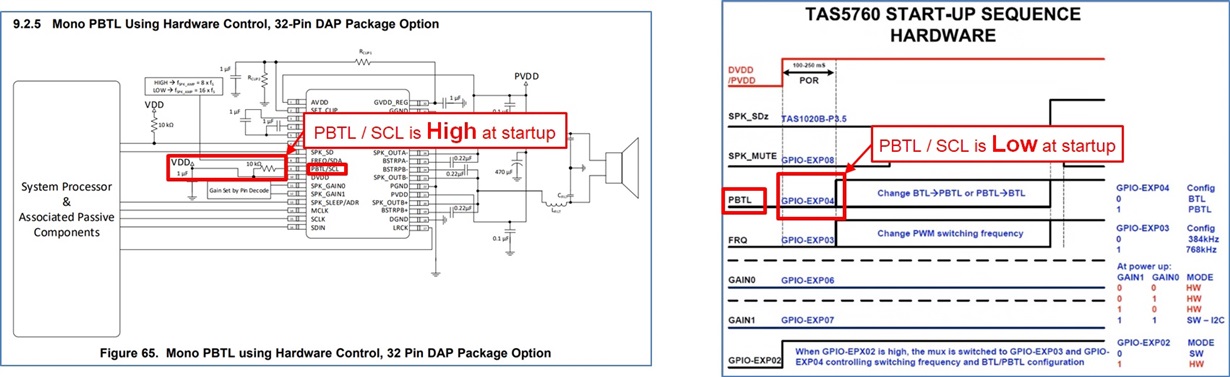

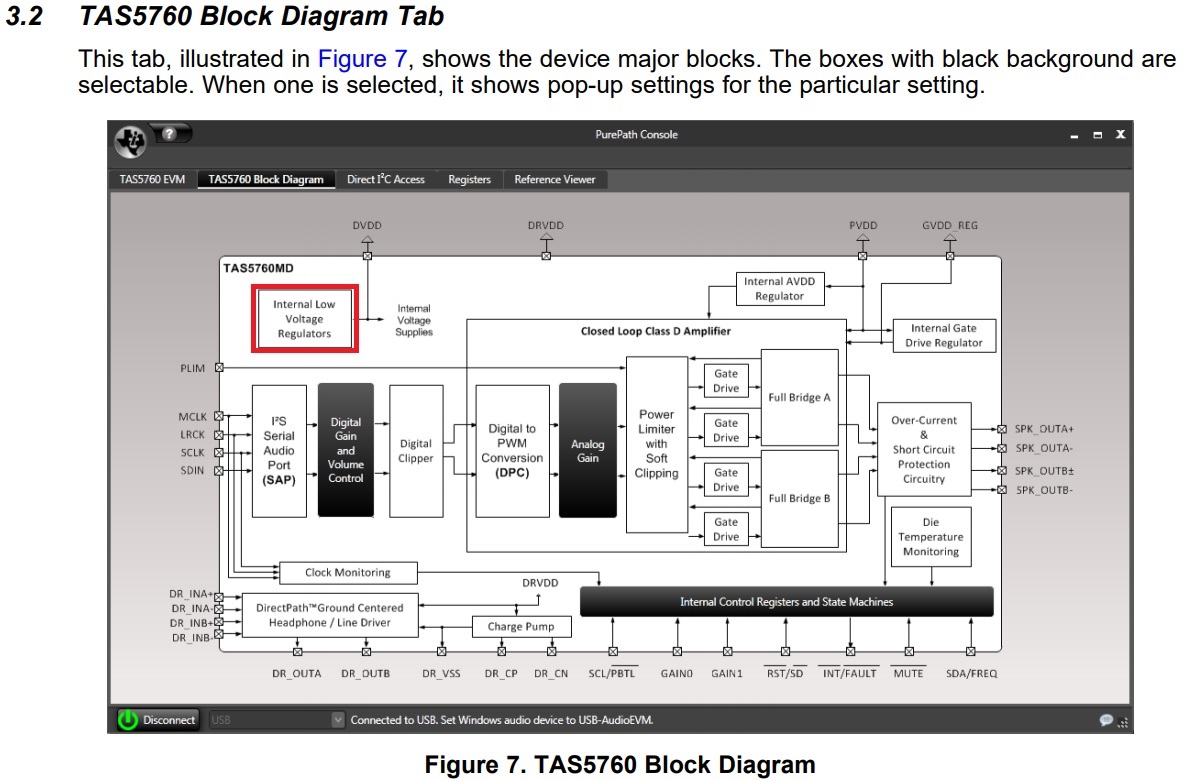

Customer designed PBTL mode with hardware control, but it seems to be booting in BTL mode.

The SPK_FAULT signal is likely to be asserted low because an overcurrent error has occurred due to an output short circuit.

So I have a question.

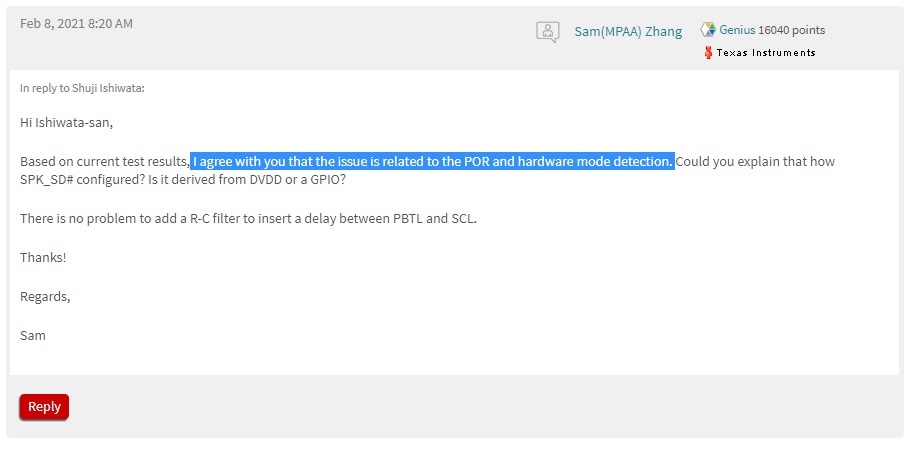

I confirmed e2e.(e2e.ti.com/.../626902)

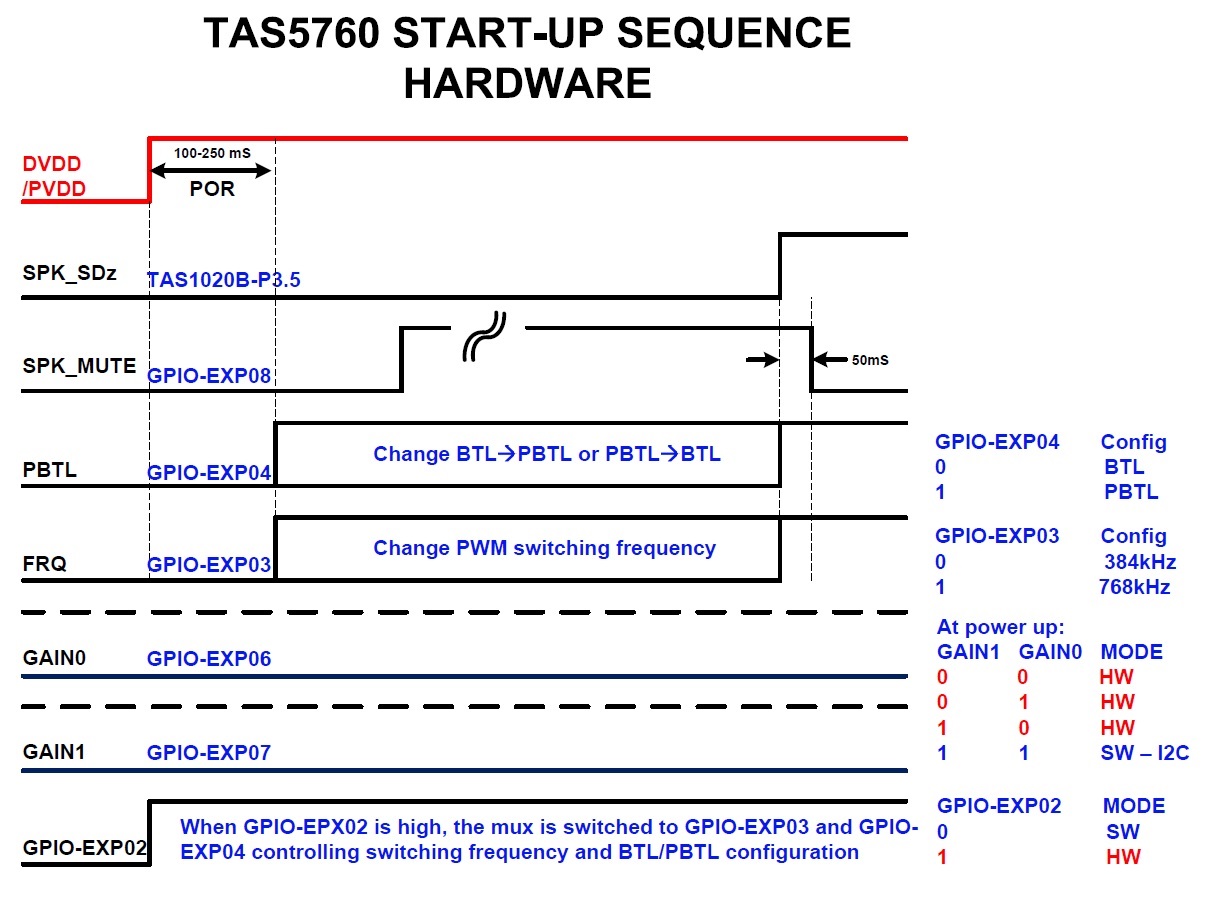

In the following sequence, DVDD and PVDD will start up and POR will operate.

If the Configuration pin is stable after 100-250ms, you can read each status.

Is this understanding correct?

Also, which of DVDD and PVDD triggers the POR?

When driving a POR circuit, the Slew Rate of the power supply may be an issue.

Are there any restrictions on the slew rate of the power supply?

Best Regards,

Ishiwata