Dear Expert,

we are using the ADC3101 for data acquisition, we use it as the slave mode , and the timing is from the external MCU timing which is 32MHz, if we want to get

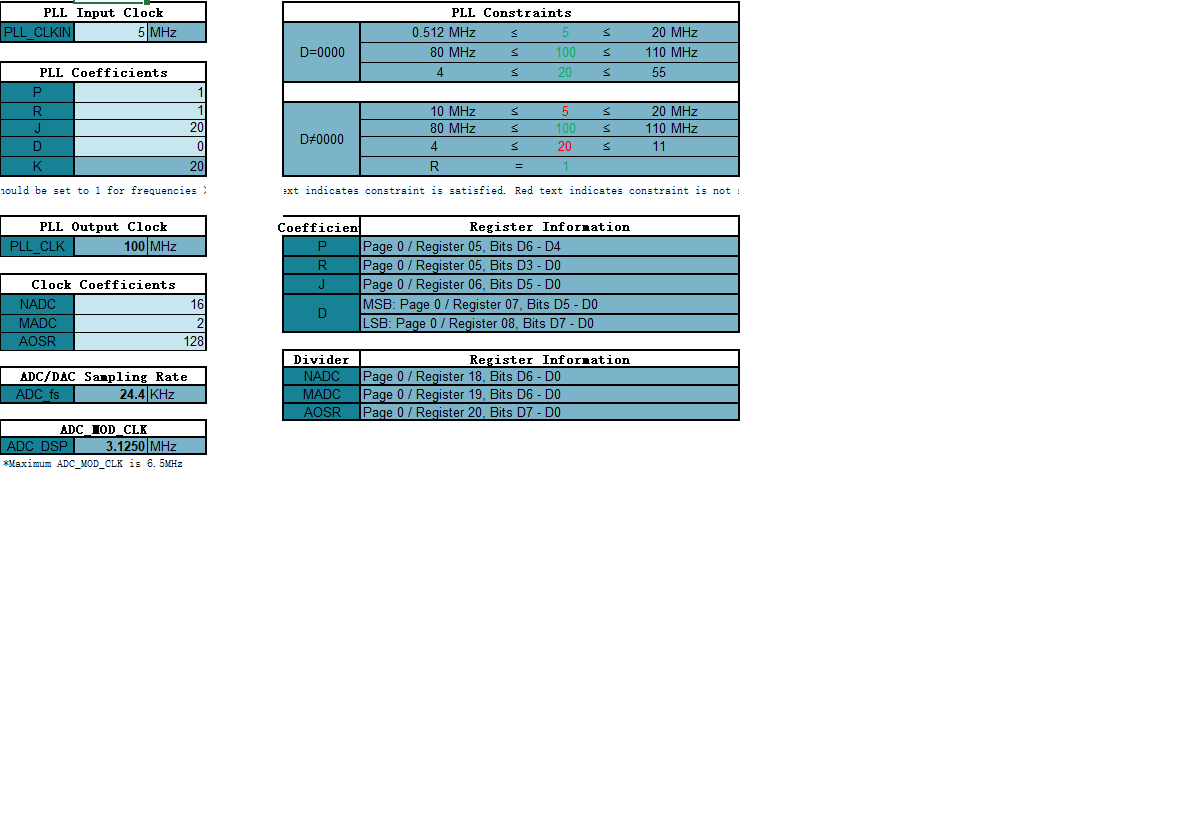

a sampling frequency of 22.05KHz fs, could you give me a setting demo about the register?

many thanks.