Hello,

We have implemented the PCM1840 ADC in several new and reworked designs. In only one case we are having heavy problems to get the converter running stable.

The problem we have:

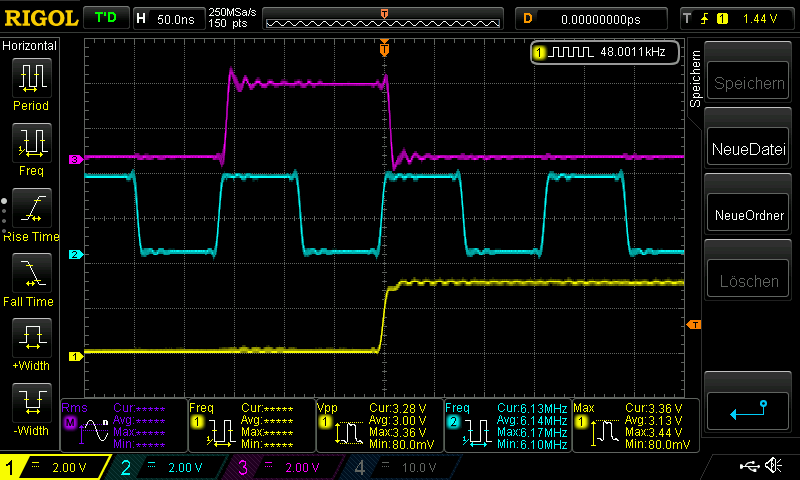

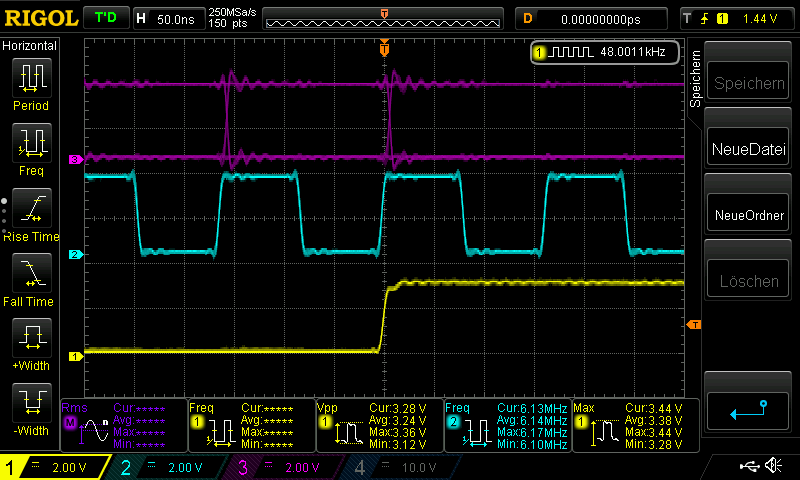

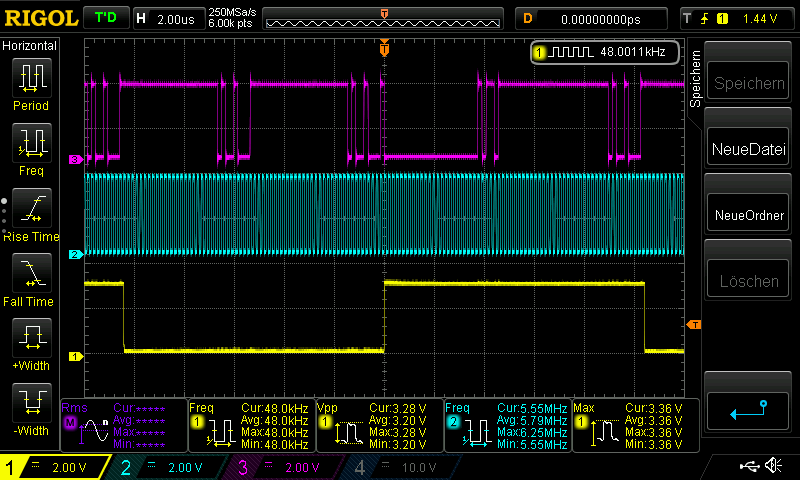

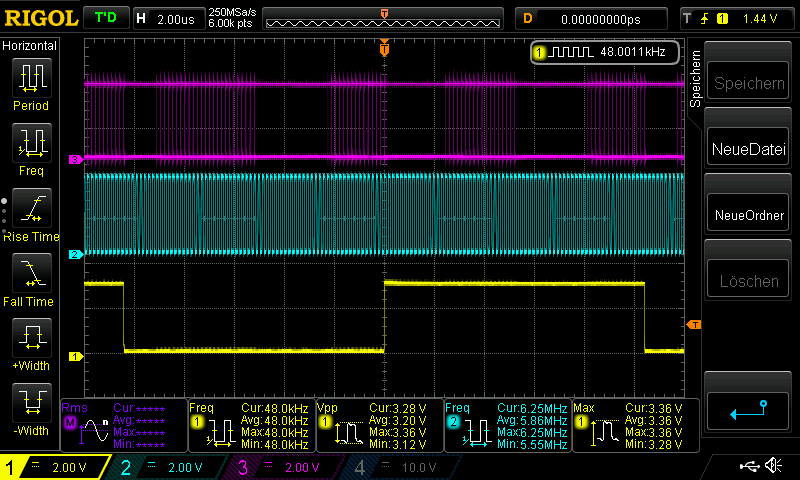

After switching on the device and booting the DSP, there is either a "broken looking" data stream or just a zero out of the ADCs. All clocks are running and looking fine.

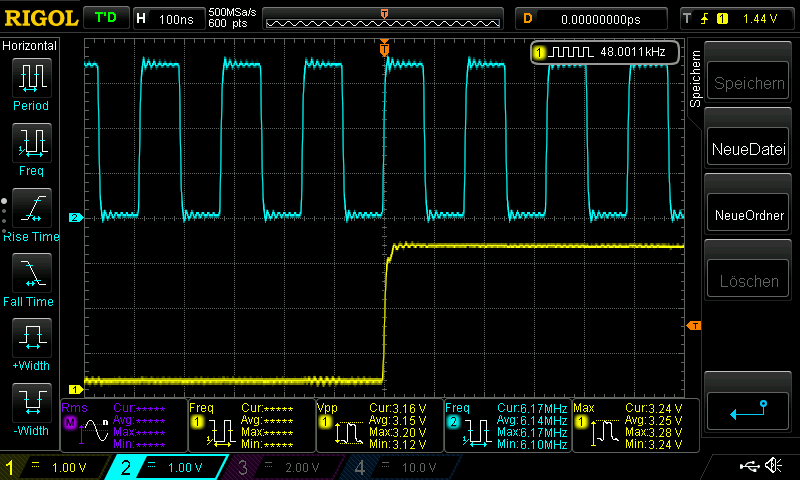

Now if I just "short" the LRCLK to ground, to skip it out for a moment and then release it, the converter starts working normal. Also if the converter is running normal and I set it to PDN, sometimes it comes up again and sometimes not. So my guess is, it might have something to do with the PLL of the converter?!

Both of the converter are acting similar and we even already replaced the parts with new ones.

The configuration:

2xPCM1840 running in TDM4 left-justified mode as slave hooked up to a ADAU1452 - one data line per converter to the DSP and a common BCLK and LRCLK from the DSP to the converters.

BCLK is running at 6.144MHz pos. Edge

LRCLK is running at 48kHz pos. Egde (right now we are running pulse mode, but also tried 50/50)

FMT1, FMT0, MSZ, MD0 are set to low

MD1 is switchable for DRE application.

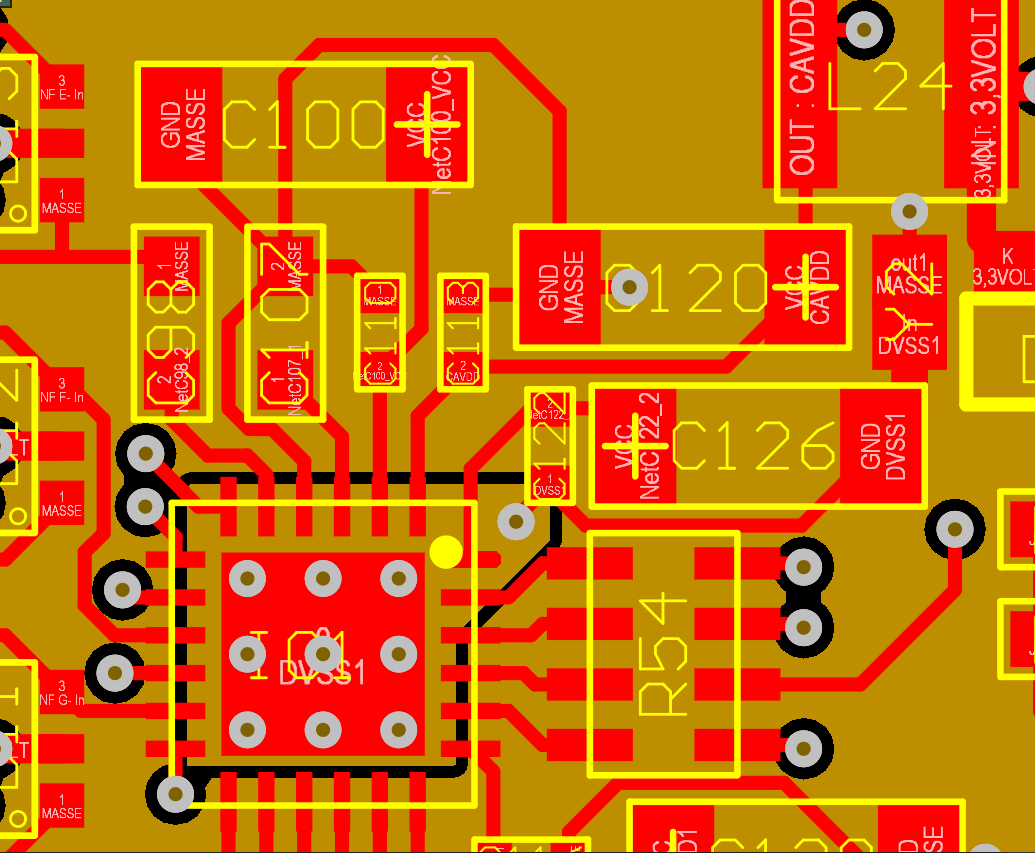

The local layout and the power supply of the ADCs is similar to our running implementations of the device, if there are some critical points in layout and power, I can point out more details on this.

Did someone have a similar problem to this or an idea how to proceed the debugging?

Thanks for your help,

Florian