Hi,

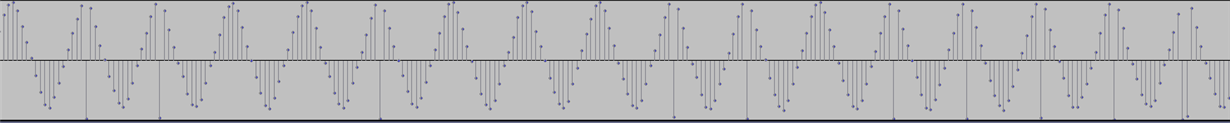

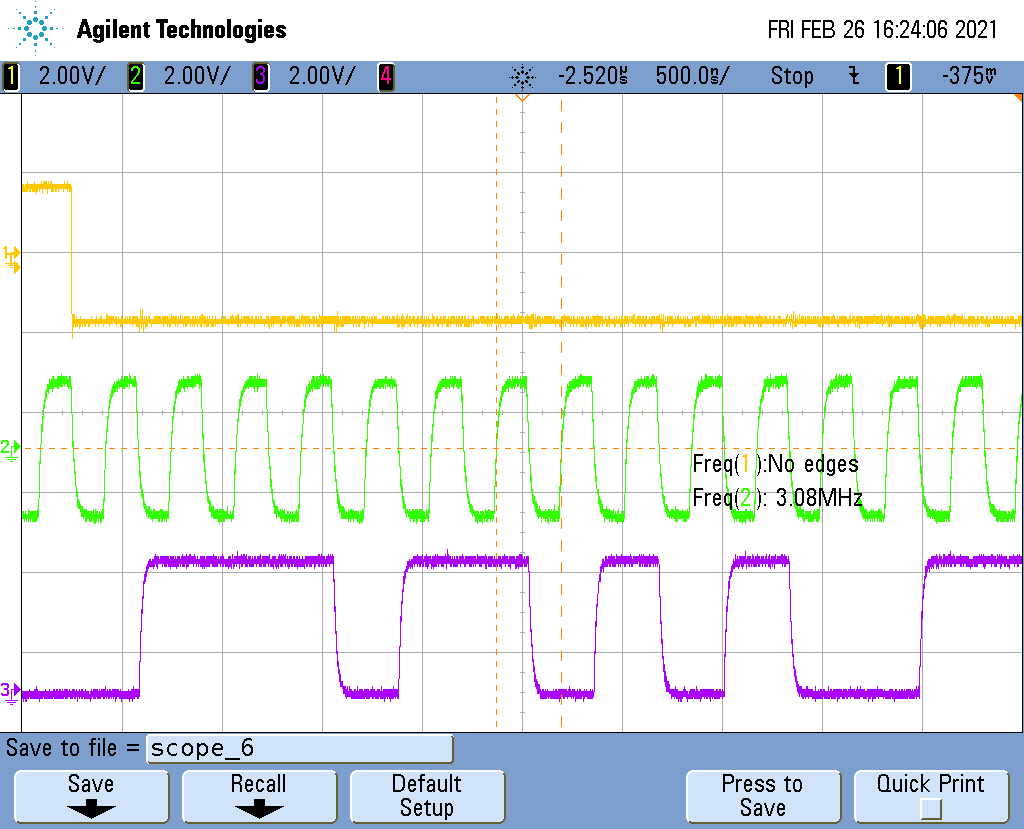

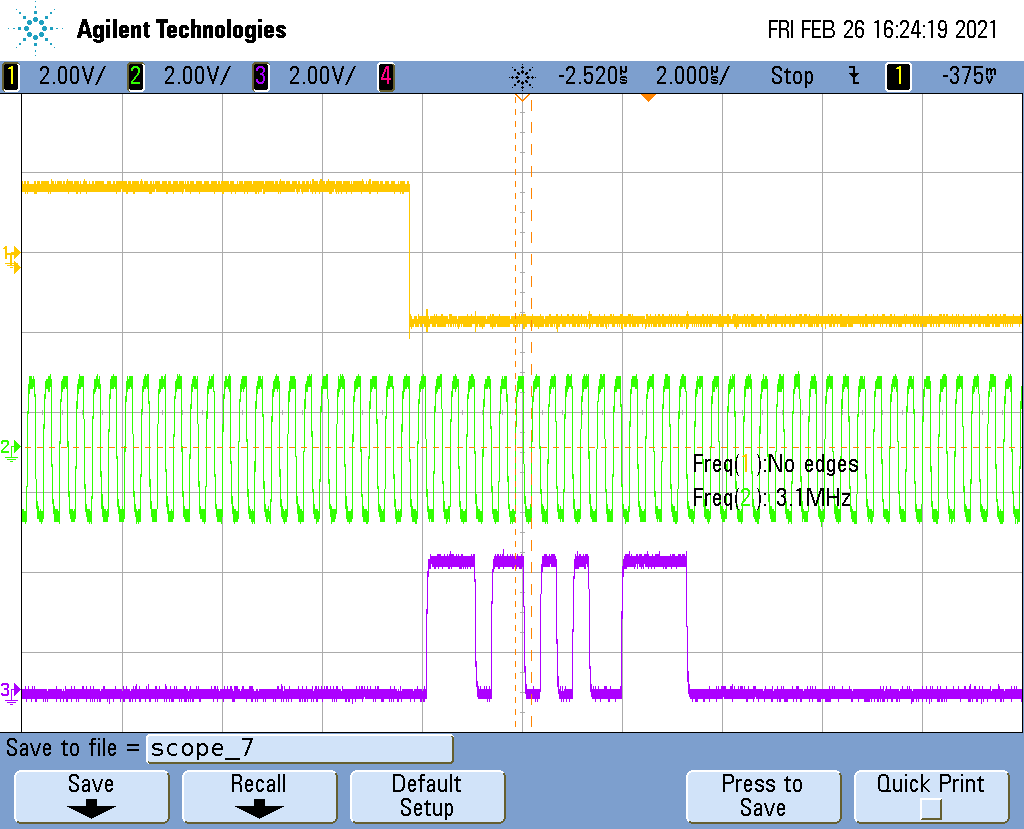

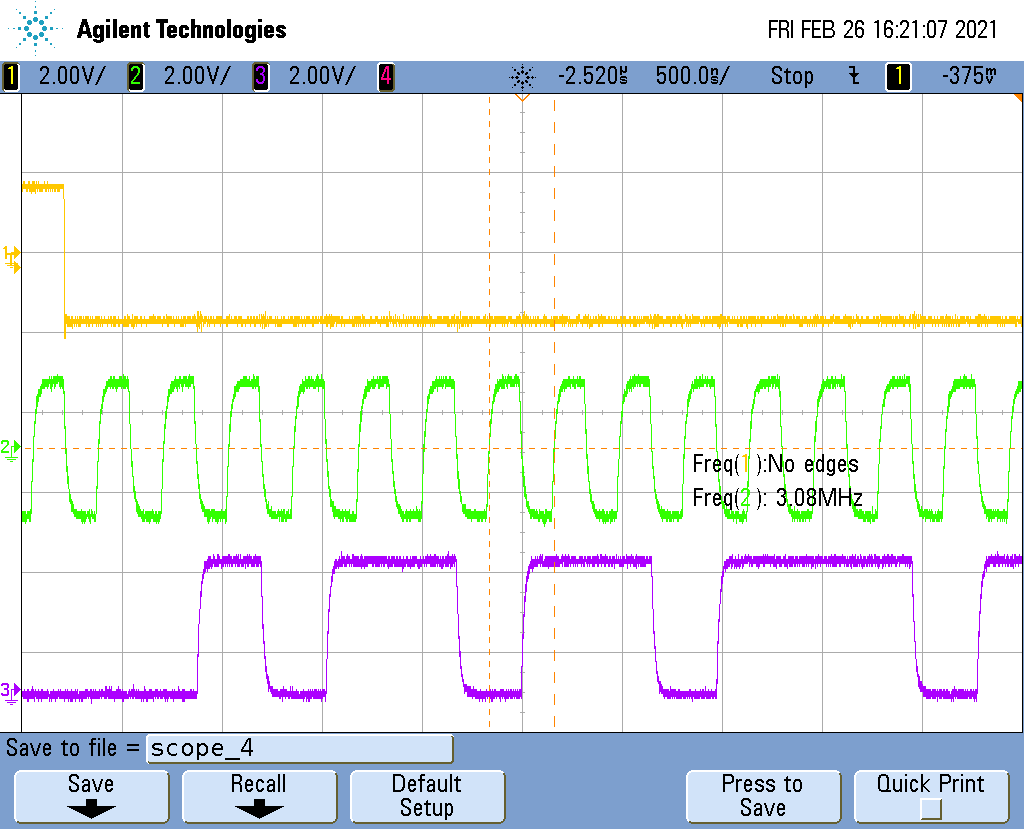

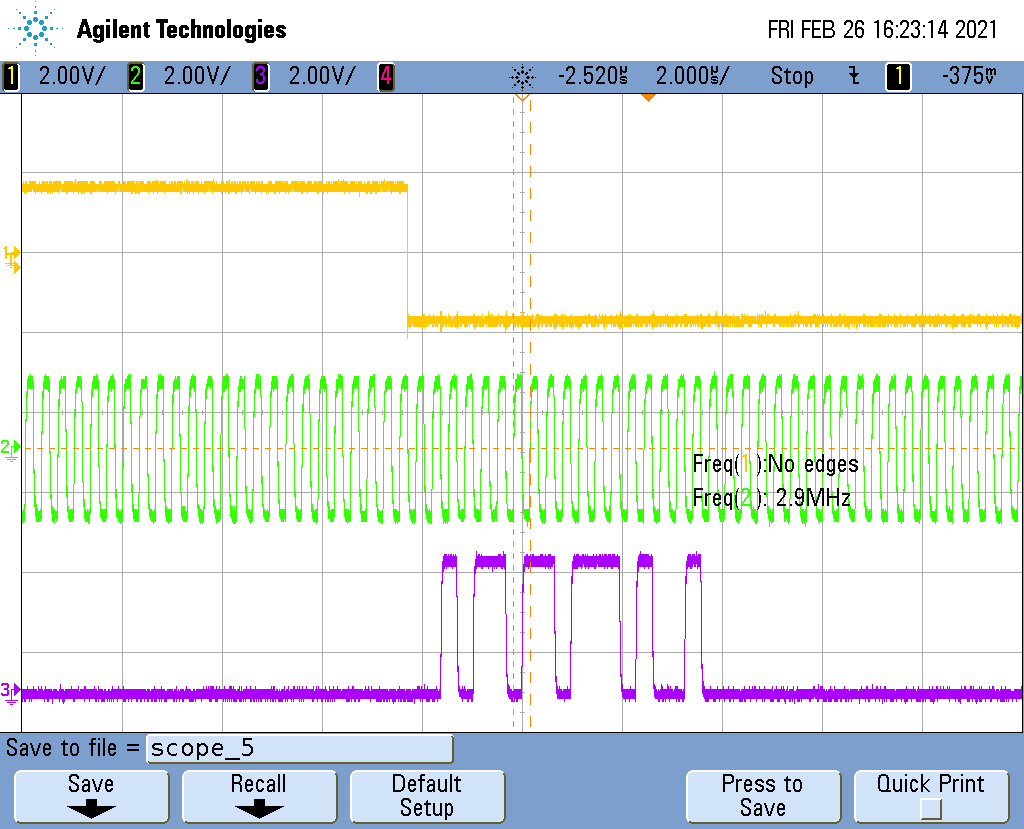

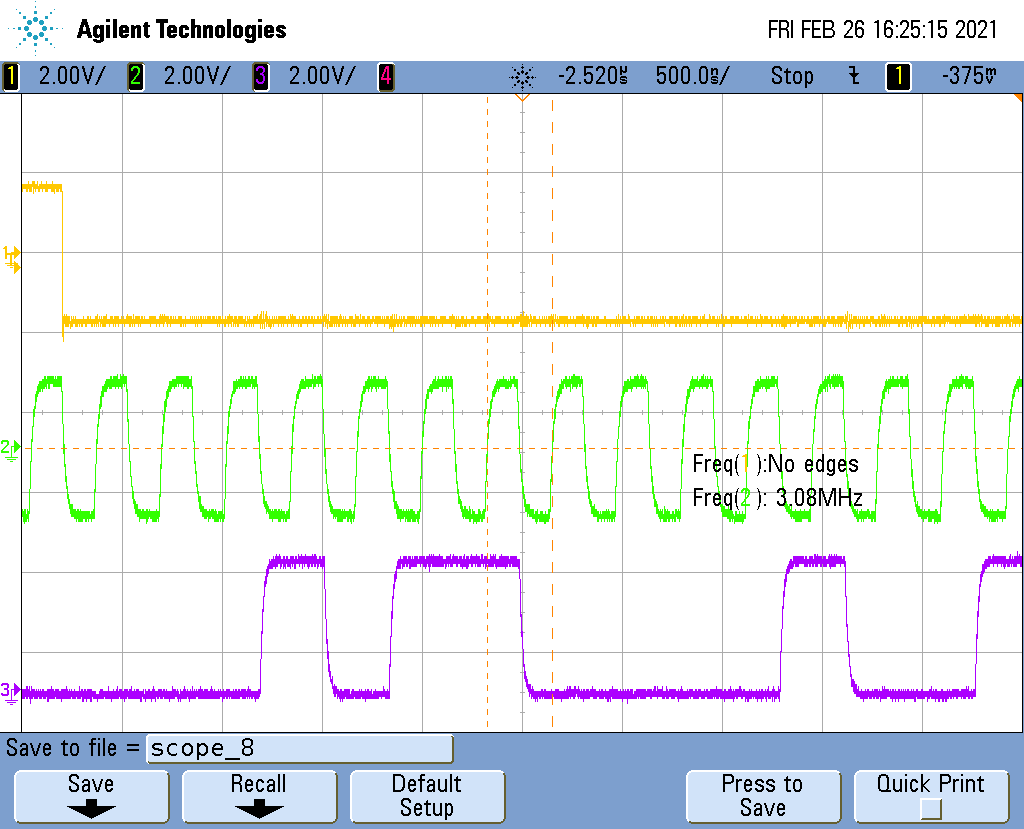

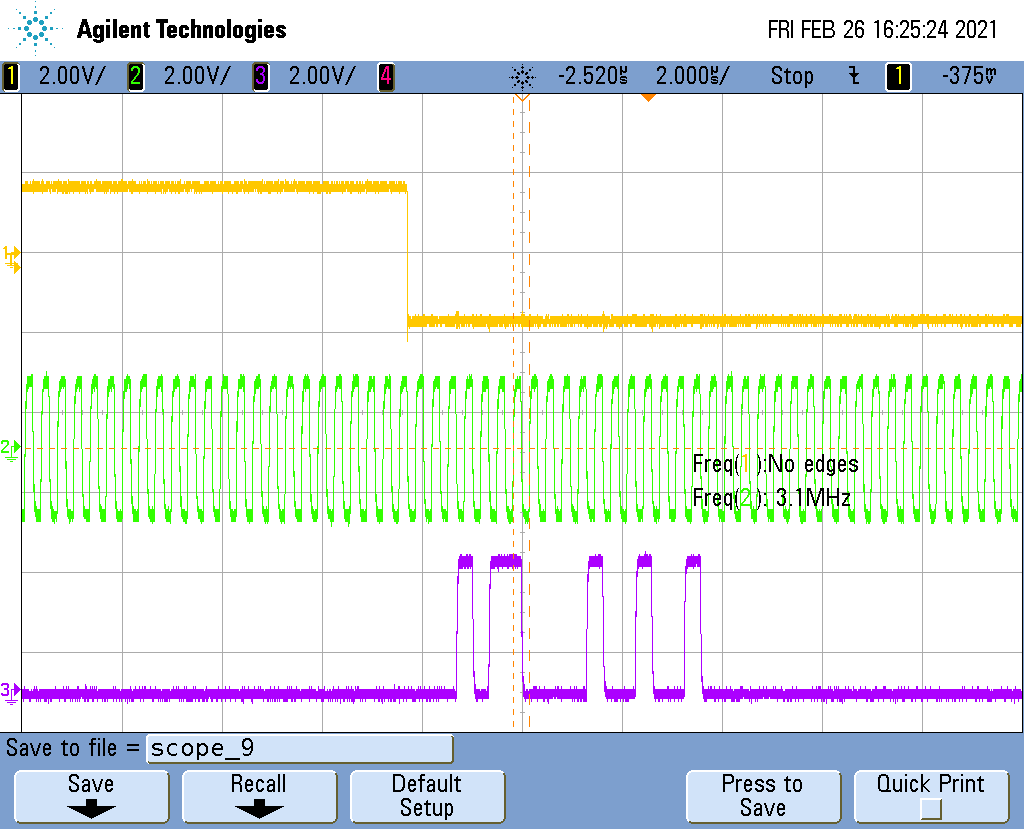

My team and I are currently observing something that we find strange. We are using the input LINE2L for our application and have verified that the input levels are in the mV range and should not be saturating the input. When we raise the PGA level, we can hear saturation in our recordings which so far is understandable. What we don't understand is when we analyze the digital data of our recordings, we observe rollovers on the digital values that exceed the peaks. We were expecting clipping instead and because of this rollover, the saturation sound more like distortion therefore sounding very bad.

Our application is running the CODEC at 32bit signed PCM with 16kHz sampling in I2S mode. Here is a figure showcasing our issue. It is a 1kHz tone captured by our microphone into LINE2L which is then digitalized. I have also attached a dump of the registers of the CODEC.

Best regards,

Alex

codec readreg 0 codec readreg 0 0x0 pts>codec readreg 1 codec readreg 1 0x0 pts>codec readreg 2 codec readreg 2 0x44 pts>codec readreg 3 codec readreg 3 0x91 pts>codec readreg 4 codec readreg 4 0x80 pts>codec readreg 5 codec readreg 5 0x0 pts>codec readreg 6 codec readreg 6 0x0 pts>codec readreg 7 codec readreg 7 0x8 pts>codec readreg 8 codec readreg 8 0x0 pts>codec readreg 9 codec readreg 9 0x30 pts>codec readreg 10 codec readreg 10 0x0 pts>codec readreg 11 codec readreg 11 0x81 pts>codec readreg 12 codec readreg 12 0x0 pts>codec readreg 13 codec readreg 13 0x0 pts>codec readreg 14 codec readreg 14 0x0 pts>codec readreg 15 codec readreg 15 0x4A pts>codec readreg 16 codec readreg 16 0x80 pts>codec readreg 17 codec readreg 17 0x0 pts>codec readreg 18 codec readreg 18 0xF0 pts>codec readreg 19 codec readreg 19 0xFC pts>codec readreg 20 codec readreg 20 0x78 pts>codec readreg 21 codec readreg 21 0xF8 pts>codec readreg 22 codec readreg 22 0xF8 pts>codec readreg 23 codec readreg 23 0x78 pts>codec readreg 24 codec readreg 24 0xF8 pts>codec readreg 25 codec readreg 25 0x86 pts>codec readreg 26 codec readreg 26 0x0 pts>codec readreg 27 codec readreg 27 0xFE pts>codec readreg 28 codec readreg 28 0x0 pts>codec readreg 29 codec readreg 29 0x0 pts>codec readreg 30 codec readreg 30 0xFE pts>codec readreg 31 codec readreg 31 0x0 pts>codec readreg 32 codec readreg 32 0x0 pts>codec readreg 33 codec readreg 33 0x0 pts>codec readreg 34 codec readreg 34 0x0 pts>codec readreg 35 codec readreg 35 0x0 pts>codec readreg 36 codec readreg 36 0xC0 pts>codec readreg 37 codec readreg 37 0x80 pts>codec readreg 38 codec readreg 38 0x0 pts>codec readreg 39 codec readreg 39 0x0 pts>codec readreg 40 codec readreg 40 0x0 pts>codec readreg 41 codec readreg 41 0x0 pts>codec readreg 42 codec readreg 42 0x0 pts>codec readreg 43 codec readreg 43 0x0 pts>codec readreg 44 codec readreg 44 0x80 pts>codec readreg 45 codec readreg 45 0x0 pts>codec readreg 46 codec readreg 46 0x0 pts>codec readreg 47 codec readreg 47 0x80 pts>codec readreg 48 codec readreg 48 0x0 pts>codec readreg 49 codec readreg 49 0x0 pts>codec readreg 50 codec readreg 50 0x0 pts>codec readreg 51 codec readreg 51 0x9F pts>codec readreg 52 codec readreg 52 0x0 pts>codec readreg 53 codec readreg 53 0x0 pts>codec readreg 54 codec readreg 54 0x80 pts>codec readreg 55 codec readreg 55 0x0 pts>codec readreg 56 codec readreg 56 0x0 pts>codec readreg 57 codec readreg 57 0x0 pts>codec readreg 58 codec readreg 58 0x9F pts>codec readreg 59 codec readreg 59 0x0 pts>codec readreg 60 codec readreg 60 0x0 pts>codec readreg 61 codec readreg 61 0x0 pts>codec readreg 62 codec readreg 62 0x0 pts>codec readreg 63 codec readreg 63 0x0 pts>codec readreg 64 codec readreg 64 0x0 pts>codec readreg 65 codec readreg 65 0x4 pts>codec readreg 66 codec readreg 66 0x0 pts>codec readreg 67 codec readreg 67 0x0 pts>codec readreg 68 codec readreg 68 0x0 pts>codec readreg 69 codec readreg 69 0x0 pts>codec readreg 70 codec readreg 70 0x0 pts>codec readreg 71 codec readreg 71 0x0 pts>codec readreg 72 codec readreg 72 0x4 pts>codec readreg 73 codec readreg 73 0x0 pts>codec readreg 74 codec readreg 74 0x0 pts>codec readreg 75 codec readreg 75 0x0 pts>codec readreg 76 codec readreg 76 0x0 pts>codec readreg 77 codec readreg 77 0x0 pts>codec readreg 78 codec readreg 78 0x0 pts>codec readreg 79 codec readreg 79 0x0 pts>codec readreg 80 codec readreg 80 0x0 pts>codec readreg 81 codec readreg 81 0x0 pts>codec readreg 82 codec readreg 82 0x0 pts>codec readreg 83 codec readreg 83 0x0 pts>codec readreg 84 codec readreg 84 0x0 pts>codec readreg 85 codec readreg 85 0x0 pts>codec readreg 86 codec readreg 86 0x0 pts>codec readreg 87 codec readreg 87 0x0 pts>codec readreg 88 codec readreg 88 0x0 pts>codec readreg 89 codec readreg 89 0x0 pts>codec readreg 90 codec readreg 90 0x0 pts>codec readreg 91 codec readreg 91 0x0 pts>codec readreg 92 codec readreg 92 0x0 pts>codec readreg 93 codec readreg 93 0x0 pts>codec readreg 94 codec readreg 94 0x84 pts>codec readreg 95 codec readreg 95 0x8 pts>codec readreg 96 codec readreg 96 0x0 pts>codec readreg 97 codec readreg 97 0x0 pts>codec readreg 98 codec readreg 98 0x0 pts>codec readreg 99 codec readreg 99 0x0 pts>codec readreg 100 codec readreg 100 0x0 pts>codec readreg 101 codec readreg 101 0x0 pts>codec readreg 102 codec readreg 102 0xA2 pts>codec readreg 103 codec readreg 103 0x0 pts>codec readreg 104 codec readreg 104 0x0 pts>codec readreg 105 codec readreg 105 0x0 pts>codec readreg 106 codec readreg 106 0x0 pts>codec readreg 107 codec readreg 107 0x0 pts>codec readreg 108 codec readreg 108 0x0 pts>codec readreg 109 codec readreg 109 0x0 pts>codec readreg 110 codec readreg 110 0x0 pts>codec readreg 111 codec readreg 111 0x0 pts>codec readreg 112 codec readreg 112 0x0 pts>codec readreg 113 codec readreg 113 0x0 pts>codec readreg 114 codec readreg 114 0x0 pts>codec readreg 115 codec readreg 115 0x0 pts>codec readreg 116 codec readreg 116 0x0 pts>codec readreg 117 codec readreg 117 0x0 pts>codec readreg 118 codec readreg 118 0x0 pts>codec readreg 119 codec readreg 119 0x0 pts>codec readreg 120 codec readreg 120 0x0 pts>codec readreg 121 codec readreg 121 0x0 pts>codec readreg 122 codec readreg 122 0x0 pts>codec readreg 123 codec readreg 123 0x0 pts>codec readreg 124 codec readreg 124 0x0 pts>codec readreg 125 codec readreg 125 0x0 pts>codec readreg 126 codec readreg 126 0x0 pts>codec readreg 127 codec readreg 127 0x0 pts>