Other Parts Discussed in Thread: PCM5102EVM-U, PCM9211EVM-U

Hi,

A customer pointed out PCM5102A has a drift of Group Delay.

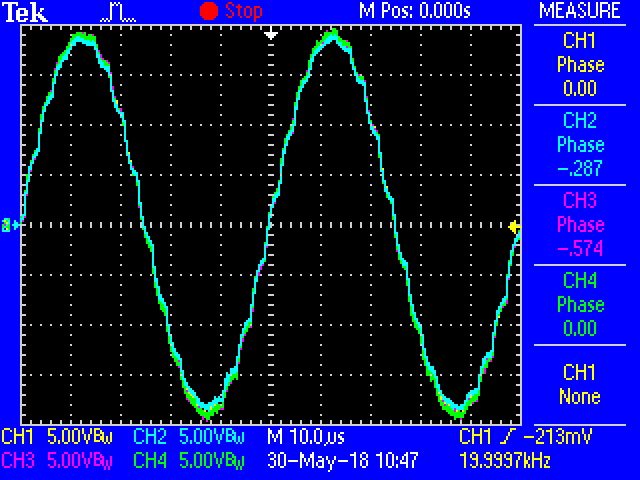

He tested using two PCM5102A, he inputted same 20 kHz sine wave signal data and clocks to them.

1L: PCM5102A-1 Left channel Output (blue)

1R: PCM5102A-1 right channel Output (cyan)

2L: PCM5102A-2 Left channel Output (magenta)

His questions are the reason why Group Delay drifts and whether the other DACs also drift.

In reference to this question, x8 Normal oversampling digital filter latency is 20ts as Typical Performance, in page 4 of datasheet.

However, in Table 4 Normal x8 Interpolation Filter of page 17, Filter group delay is 22ts. Which value is correct?

Best regards,

Akio Ito