Other Parts Discussed in Thread: REG101, REG102, REG103, REG104

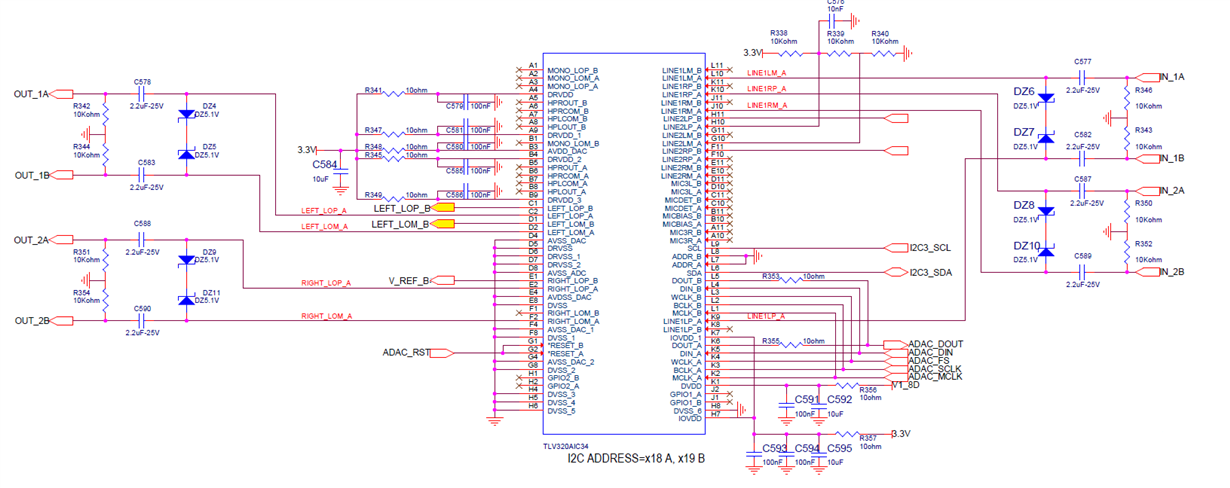

On my board I have the CODEC TLV320AIC34 for stereo audio interface (A section) and to generate constant polarization signals (B section), 16KHz sampling rate, DSP interface.

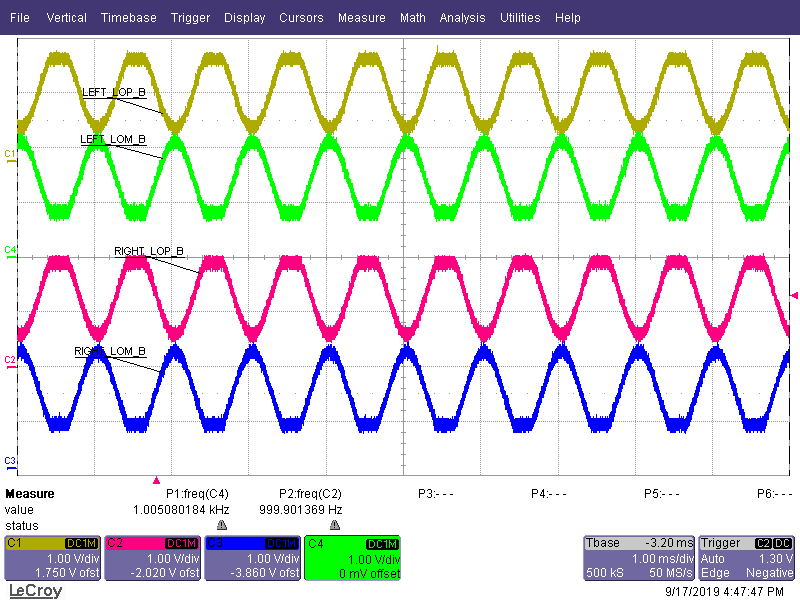

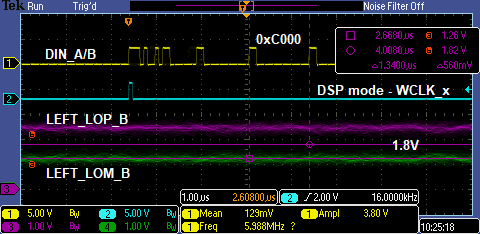

- I have noticed a sign inversion on the output of signals LEFT_LOP_B/LEFT_LOM_B: when I send a positive value (16bit: 0x2000) on the DIN interface I would expect LEFT_LOP_B> LEFT_LOM_B actually LEFT_LOM_B> LEFT_LOP_B and vice versa when I write a negative value (16bit: 0xe000). Am I doing something wrong?

- In case of a single ended output, can I use only one RIGHT_LOP_B output and leave the LEFT_LOM_B output floating?

- In the DAC section, I use DAC_L3 connected to LEFT_LOP_A / LEFT_LOM_A and DAC_R3 connected to RIGHT_LOP_A / RIGHT_LOM_A. How can I enable digital effects filters in the DAC section? Is it enough to set the coefficients on page 1 or there is some registers on page 0?

Thanks

Francesco