Hi,

I'm recording audio using TLV320ADC and ESP32. The recorded audio is fine noise-wise, however it looks as if the signal is discretized at 8 times lower rate - each sample in the i2s data is repeated 8 times.

I'm targeting 2channel 16bit audio at 22050Hz; I've set up I2S connection with BCLK, WCLK and DATA connected(No MCLK);

I2S config:

static const i2s_config_t i2s_config = {

.mode = (i2s_mode_t)(I2S_MODE_MASTER | I2S_MODE_RX),

.sample_rate = SAMPLE_RATE,

.bits_per_sample = I2S_BITS_PER_SAMPLE_16BIT,

.channel_format = I2S_CHANNEL_FMT_RIGHT_LEFT,

.communication_format = I2S_COMM_FORMAT_I2S_MSB,

.intr_alloc_flags = 0, // default interrupt priority

.dma_buf_count = 32,

.dma_buf_len = 1024,

.use_apll = true,

.tx_desc_auto_clear = false,

.fixed_mclk = 0

};

And TLV registry setup:

tlv320_selectPage(0); i2c_write_reg_byte(1, 0x01); // reset vTaskDelay(20 / portTICK_PERIOD_MS); // give it 20ms i2c_write_reg_byte(4, 0x05); // Clocl-gen multiiplexing - Use BCLK clock coming from ESP via I2S i2c_write_reg_byte(5, 0x11); // Disable PLL i2c_write_reg_byte(18, 0x81); // NADC = 1, divider powered on i2c_write_reg_byte(19, 0x82); // MADC = 2, divider powered on i2c_write_reg_byte(27, 0x00); // mode is i2s, wordlength is 16, slave mode (default) i2c_write_reg_byte(61, 0x01); // Use processing block 1 tlv320_selectPage(1); i2c_write_reg_byte(52, 0xfc); // Left ADC Input selection for Left PGA = IN1L(P) as Single-Ended i2c_write_reg_byte(55, 0xfc); // Right ADC Input selection for Right PGA = IN1R(M) as Single-Ended i2c_write_reg_byte(59, 0x00); // Left Analog PGA Seeting = 0dB i2c_write_reg_byte(60, 0x00); // Right Analog PGA Seeting = 0dB tlv320_selectPage(0); i2c_write_reg_byte(81, 0xC2); // Power-up Left ADC and Right ADC i2c_write_reg_byte(82, 0x00); // UNMUTE

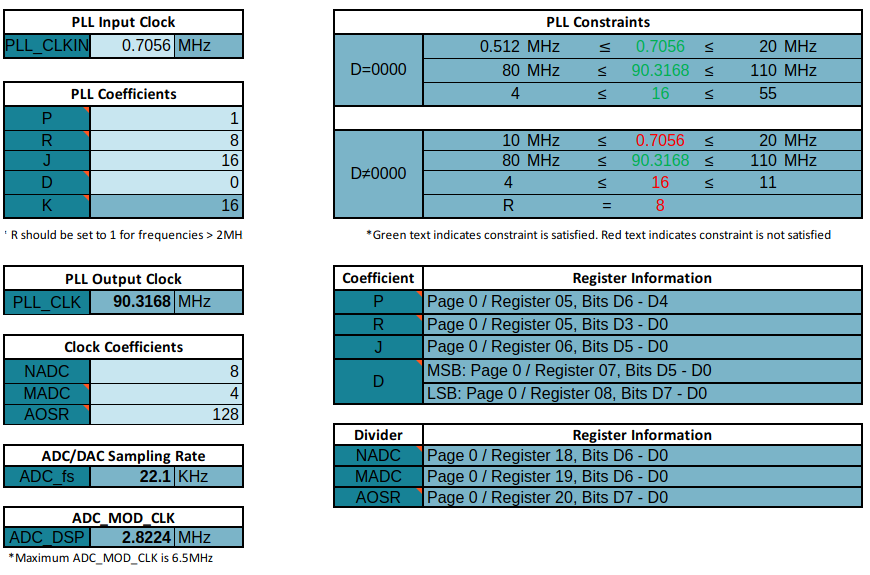

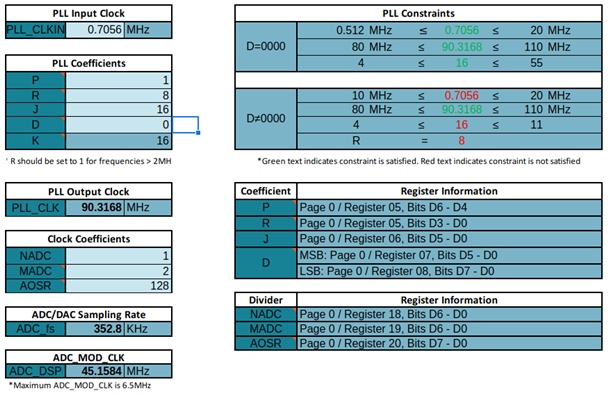

I tried enabling tlv's PLL using: P: 1 R: 8 K: 16 NADC: 8 MADC: 4 AOSR:128 but it didn't yeild any useful results.

Any help getting the TLV to record with better quality is welcome.