Hi,

My customer is evaluating the TLV320AIC3101.

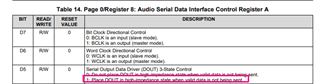

They set "1" into the register 8 D5 bit and DOUT is pulled down via a resister.

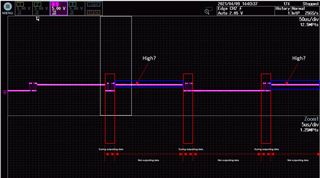

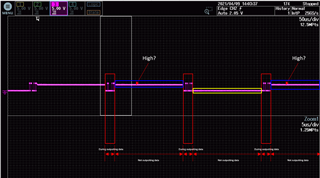

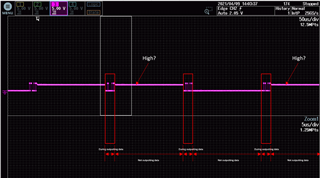

However, DOUT outputs as below High during valid data is not being sent.

Is this correct behavior?

Best Regards,

Kuramochi