Hello.

When I was designing the PCB I used a software (not sure if TICS or the EVM software) to plan the output frequencies.

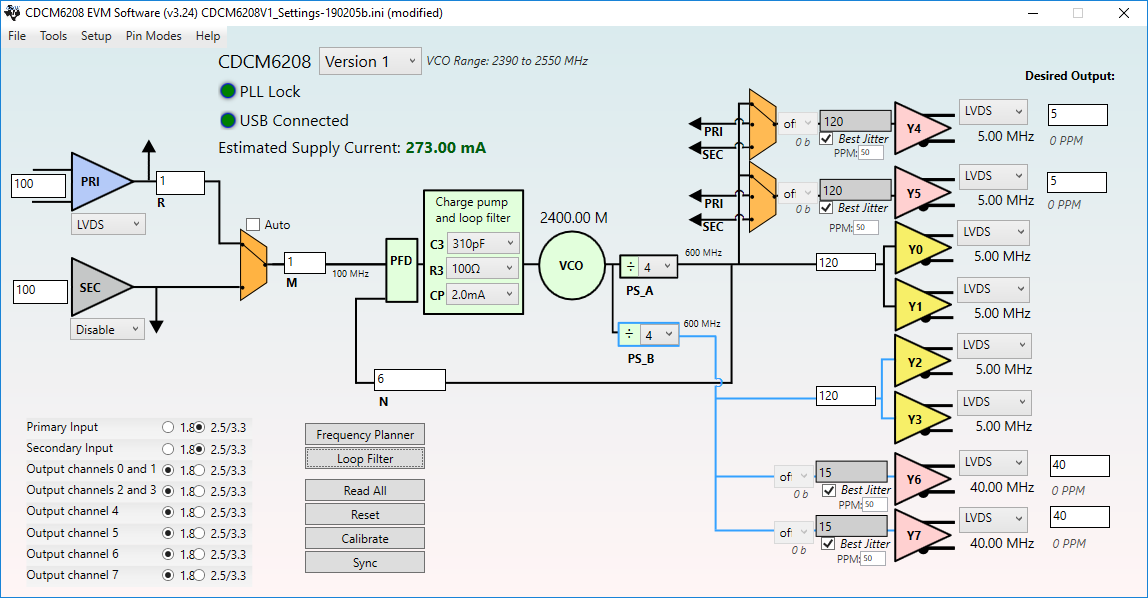

While I was creating the register stream using the EVM software, I found I could not configure the outputs like I designed in my hardware. I need six ouputs with 5MHz and two with 40MHz. Y4 and Y5 should be 50MHz, all the others should be 5MHz. However, after trying the frequency planner it does not produce the expected results, i.e. setting Y4 and Y5 to 40MHz and Y6/Y7 to 5MHz.

I tried to change the order on frequency planner but it usually sets Y6 and Y7 to 40MHz no matter the order.

I can set the outputs by manually editing the registers values. Is there any reason for this choice of outputs in terms of performance (e.g. jitter)? Is there a way to force the software to produce the outpus with the planner?