Hi

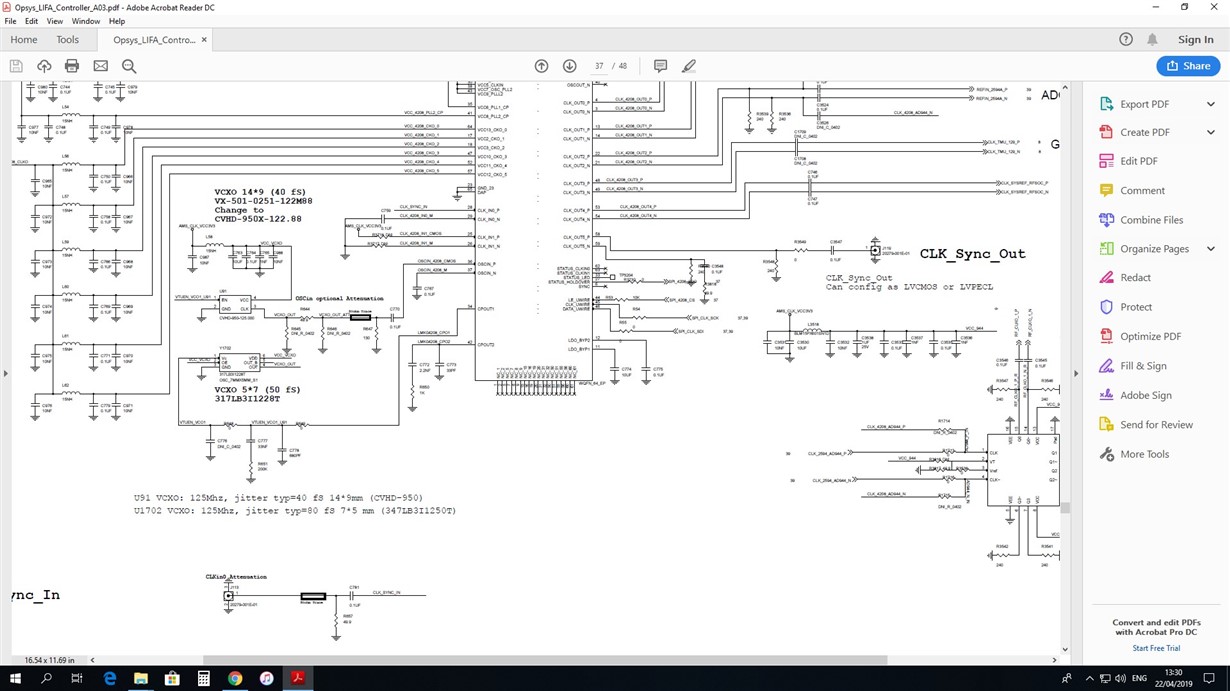

At our design we use LMK04208 to drive Xillinx FPGA in similear design as LMK04208 eval with external VCXO . We are using two similar cards when the first card is master which run as stand along mode with the below config file, and second card as slave where the master 125Mhz sync clock drive the slave clk_in_0 input.

We got 4 running card which each of them can act as slave (where it lock to the master 125Mhz clock) but one of the 4 cards fail to push (as master) the other 3 cards!!!

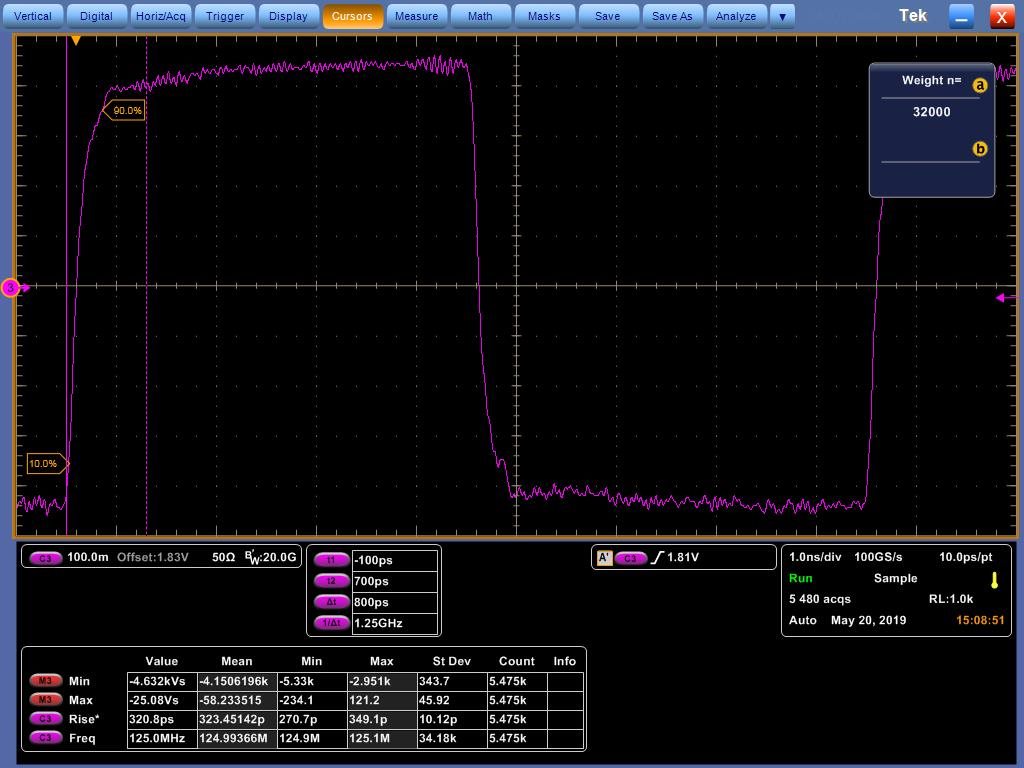

When looking with 20Ghz scoop on the LMK04208 output we almost dont see any differences

Do you got any idea what can cause this issue?

How can we inspect the jitter output of LMK04208??

The master config (where for slave config we change only input from clk_in_1 input to clk_in_0 input) :

R0 (INIT) 0x00160040

R0 0x00140300

R1 0x00140301

R2 0x00140062

R3 0x80140603

R4 0x00140304

R5 0x80140185

R6 0x01100006

R7 0x01300007

R8 0x04010008

R9 0x55555549

R10 0x9102410A

R11 0x0401100B

R12 0x1B0C006C

R13 0x2302826D

R14 0x0200000E

R15 0x8000800F

R16 0xC1550410

R24 0x00000058

R25 0x02C9C419

R26 0xAFA8001A

R27 0x10001E1B

R28 0x00201E1C

R29 0x0180019D

R30 0x0200019E

R31 0x003F001F

Thanks

Oded