Hello, Team,

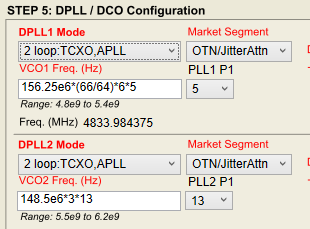

My customer is tring to use DCO mode of LMK05028. The costomer would like to use DCO without clock. We have a few questions for 2-loop TCXO-DPLL mode.

1. Could you review the below configuration? Please let me know if there is any concerns.

There is "Run cancelled. DPLL[1,2] missing input assignment" error for this configuration.

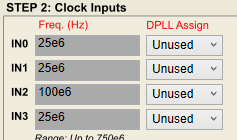

2. The customer would like not to use IN0~3 DPLL assign, but there is error message “DPLL[1,2] missing input assignment” Is it possible not to use IN0~3?

3. An error occurs when PLL1 and PLL2 are interchanged. When CH0-3 is assigned to PLL1 and CH4-6 is assigned to PLL2, there is error message “OUT [4: 7] bank need 1+ clock from PLL1”. What is this error?

I will send the TCS file, if you need.

Best Regards

Satoshi Yone