Hi Timothy,

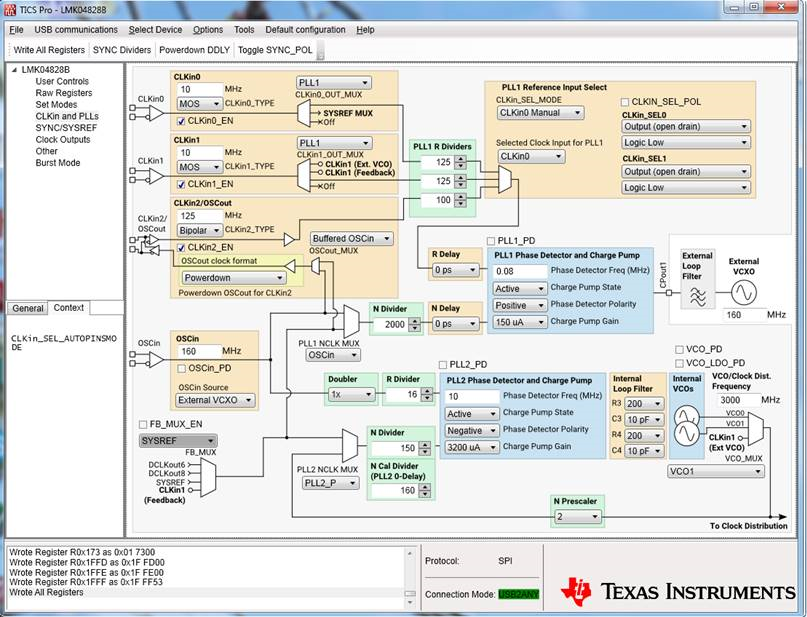

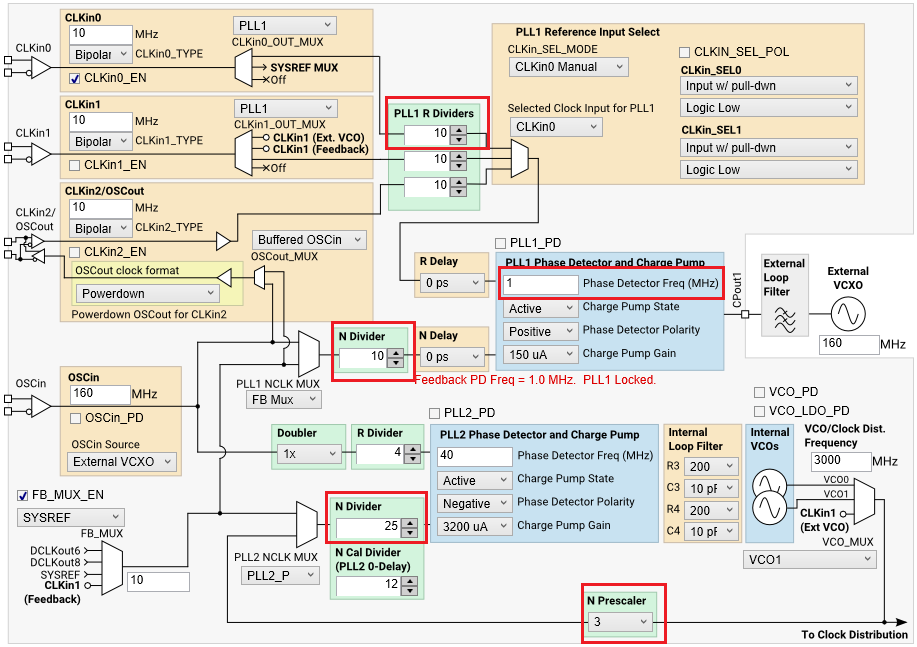

On our LMK04828 board, if in the dual loop mode, with below settings, PLL1 can be in lock consistently.

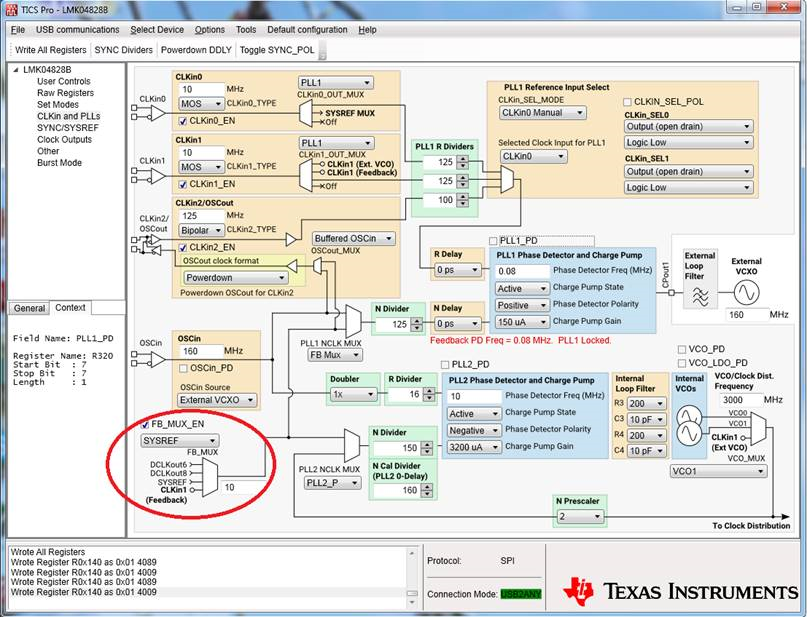

If on the Nested 0-Delay mode and kept the same PLL1 Fpd and charge pump setting, PLL1 can’t be in lock.

Until toggled the “PLL1_PD” or “PLL2_PD”, PLL1 can be in lock. Actually toggling "FB_MUX_EN" also works.

Could you help to explain this issue?

Thanks,

Jin