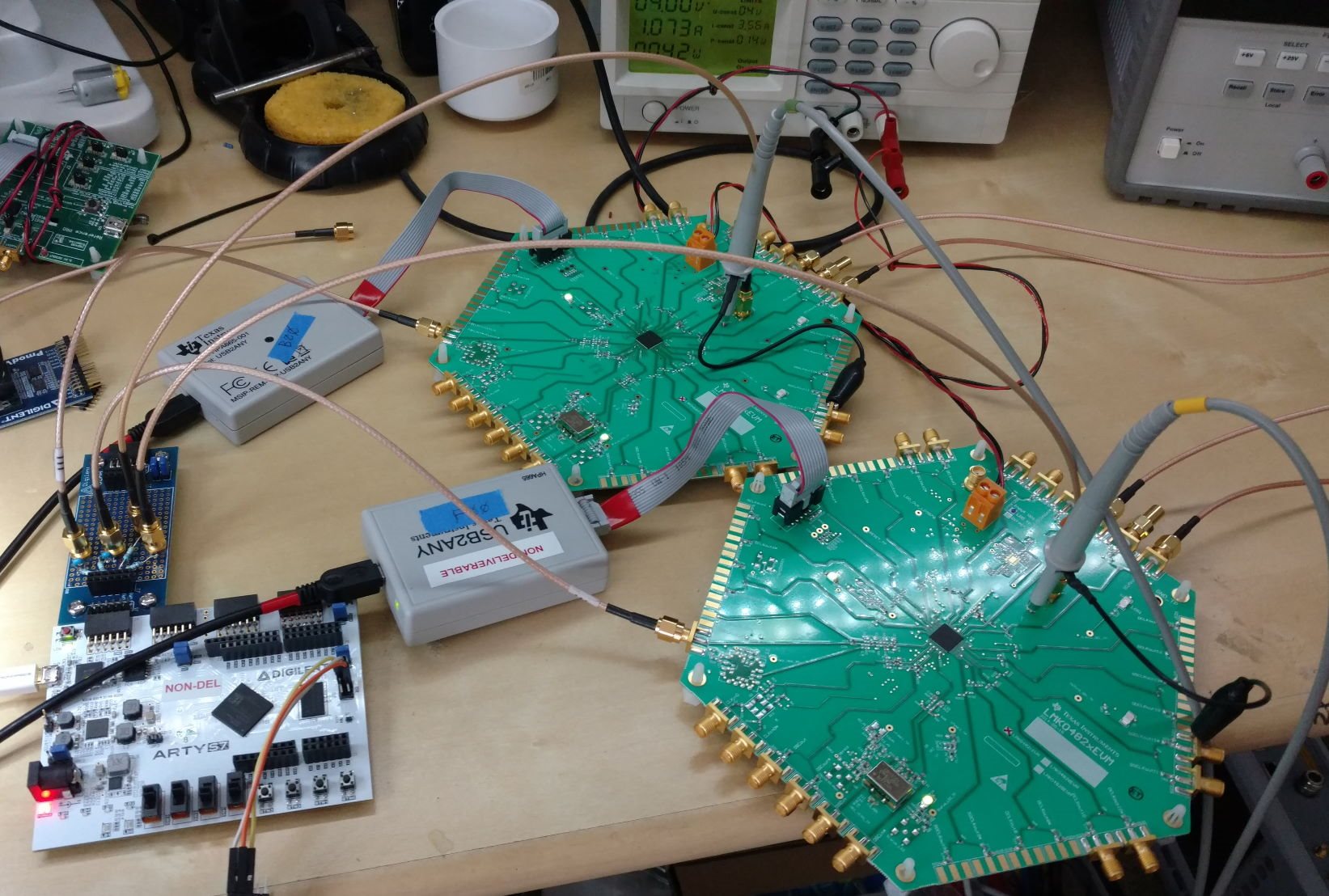

I have a pair of LMK04821EVM eval boards. I've replaced the VCXO with a 50MHz part on each (p/n CVHD-950X-50.000) and installed the SYNC input SMA connectors. I'm using a small FPGA eval board to generate some test waveforms - a 100MHz reference clock and a 1PPS signal I'm using to trigger the SYNC input. My test setup is attached, along with the configuration file I'm loading into both boards.

Both PLLs on both boards are locking and generating 100MHz outputs as expected. Both 100MHz outputs are in-phase since I have the parts configured in nested zero-delay mode (one goal is to have the 100MHz reference clock outputs in phase across multiple LMK's).

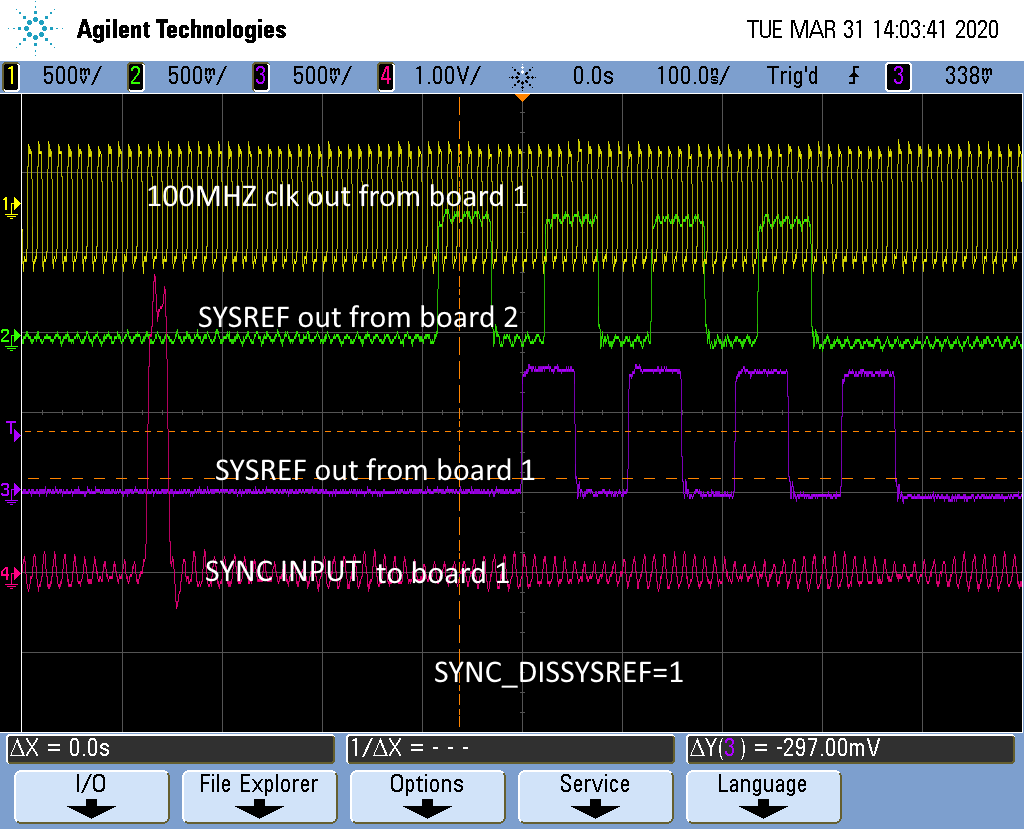

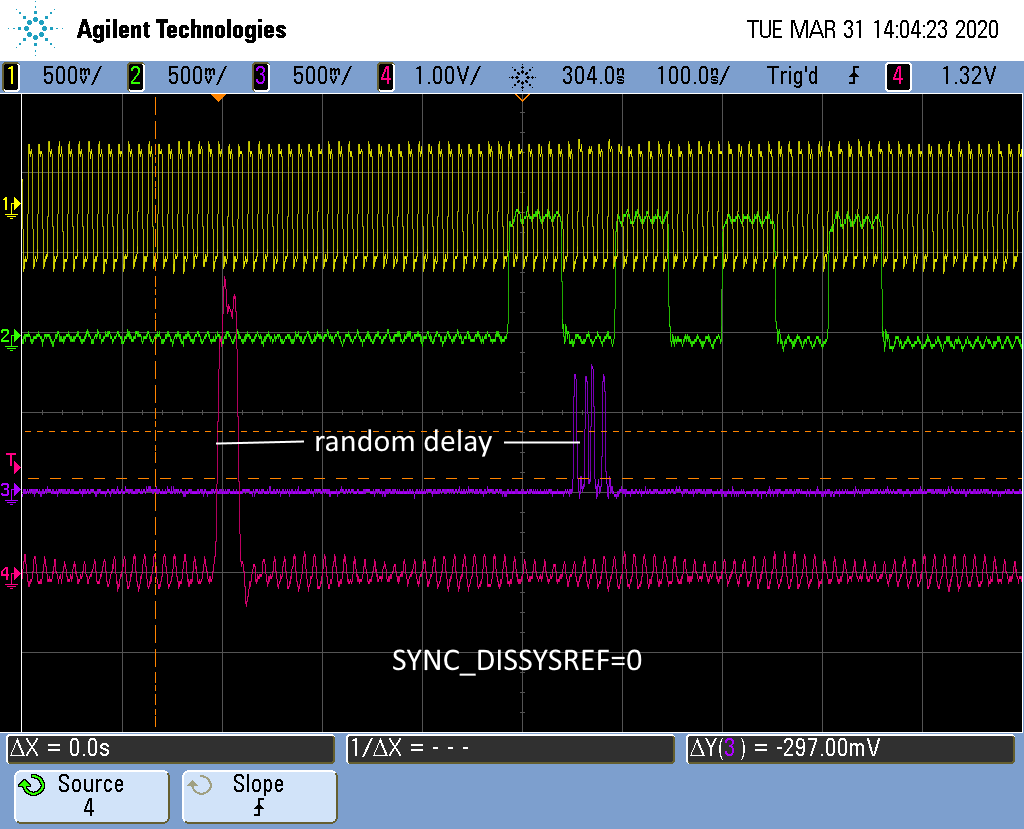

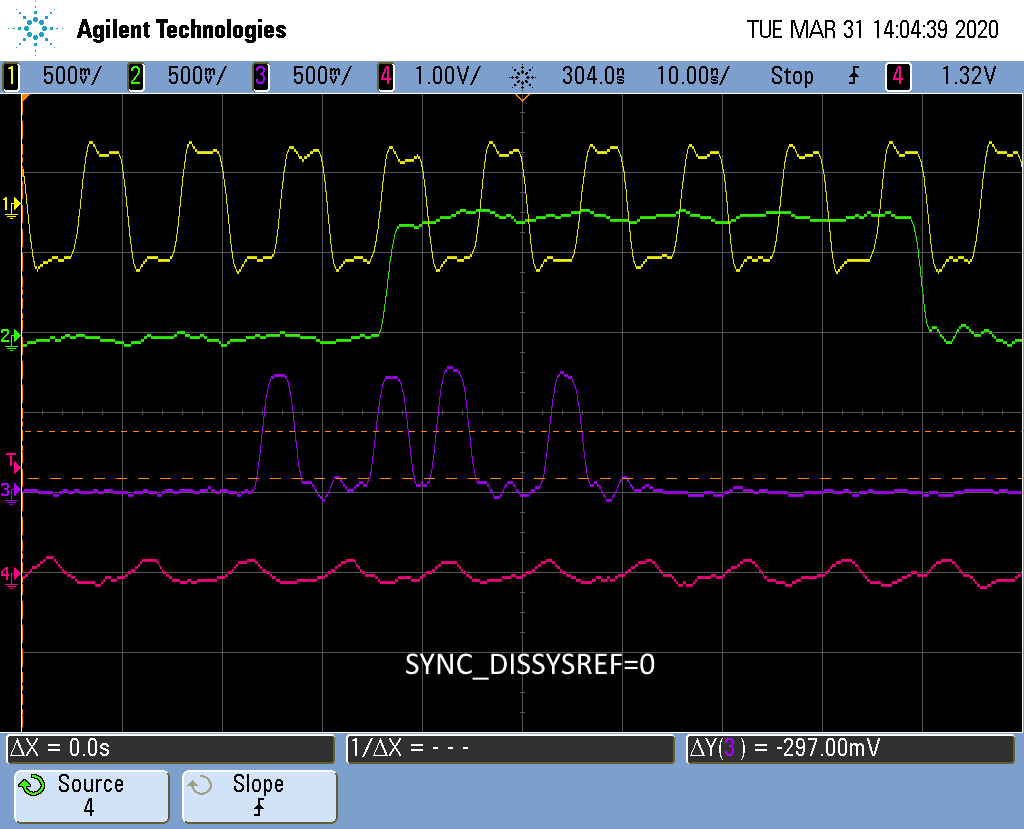

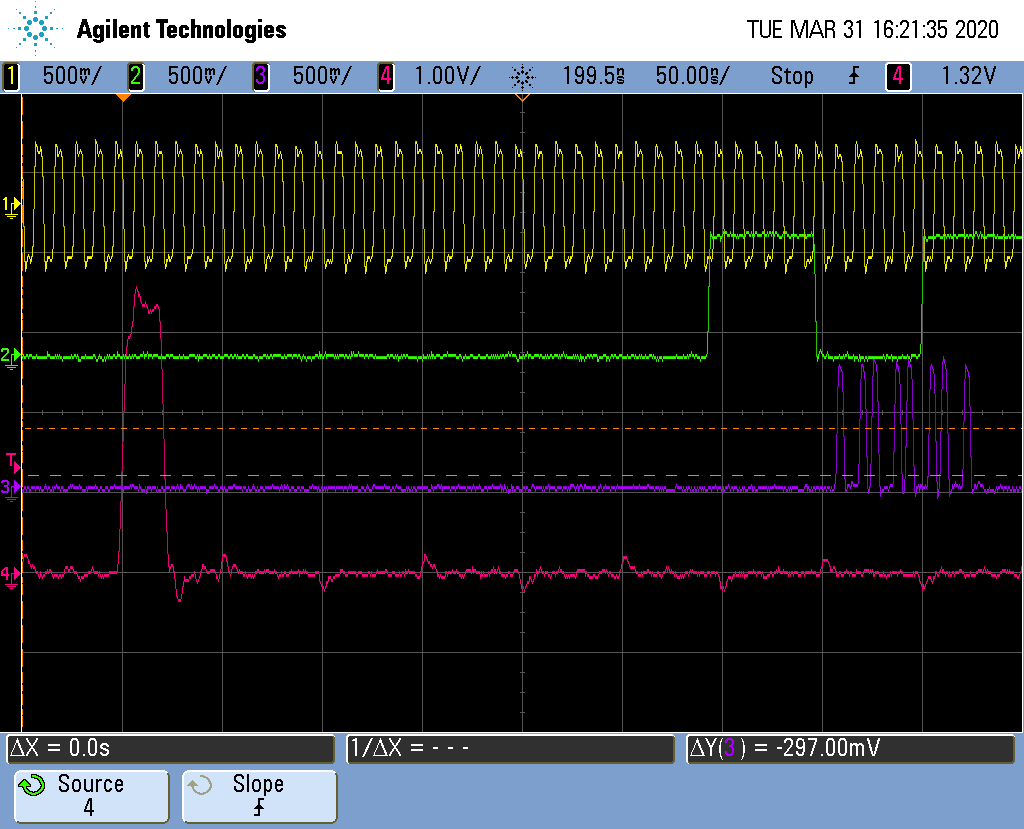

My problem is with the SYSREF outputs. I have the LMK's configured to generate 4 SYSREF pulses when a SYNC input is received. This is working ok, but the pulses-trains are randomly phased, which I understand to be due to having SYNC_DISSYSREF set. However, if I clear SYNC_DISSYSREF my SYSREF output becomes a strange burst of pulses shown on the attached plot. The number of pulses matches SYSREF_PULSE_CNT, but the time between the SYNC input and the start of the pulsetrain moves randomly after each SYNC input.

I realize there is some electrical noise in this setup - my overall grounding and signal generation isn't the greatest (making due with what I have while working from home :). But the LMK is in lock, and it seems to be receiving the SYNC input.

Any idea what's going on?