Other Parts Discussed in Thread: TIDA-01021

Hello,

We're facing an issue trying to synchronize data converters on multiple boards.

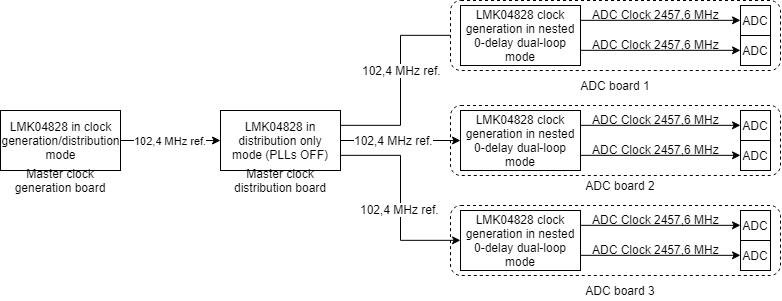

We have several boards, each of them with two high-speed JESD-204B ADCs each. These boards have an LMK04828B as their clock generator/distributor for both ADCs. The ADC sampling clock is 2457,6 MHz, sent directly from the LMK04828B, output 10 for one ADC, output 12 for the other.

These LMK04828Bs on the ADC boards are configured in nested 0-delay mode. PLL1 has a Fpd of 1024 kHz and uses a Crystek CVHD-950 122,88 MHz VCXO. PLL2 has a Fpd of 122,88 MHz, with the reference coming directly from PLL1. The loop is internally closed from output 6, at 102,4 MHz, which is the lowest frequency for any output.

The PLL1 reference for these LMK04828Bs is external at 102,4 MHz and comes from a master clock distribution board, which also uses an LMK04828 in clock distribution mode (what comes from CLKIN1 goes to every DClk output, and whatever comes from CLKin0 is broadcast to the SDClk outputs.

The input from the master clock distribution board comes from the master clock generation board, which again uses an LMK04828B, which among other things generates the 102,4 MHz reference and SYSREF that goes to the clock distribution board and is distributed to every ADC clock.

Something like this:

The SYNC/SYSREF signal follows the same path. The master clock generation board self-synchronizes its outputs, then it broadcasts a SYNC pulse via the clock distribution board, causing the simultaneous alingment of all ADC board clock outputs, and then everything is reconfigured to switch to SYSREF functionality, and the JESD link goes up witth deterministic latency and our ADCs get time-synchronized and start sampling.

To test this, we insert a pulsed sinusoidal signal directly at the ADC inputs, coming from a signal generator using a splitter and relatively equal length cables. We trigger several thousands of simultaneous captures from all ADCs and analyze them. We see the pulsed signals and compare the skew between the instants when each captured pulse starts and ends. There, we see small invariant delays, which come from the length difference between the cables and such. This delay remains constant between captures with only residual variance. This system tolerates these skews and can compensate for them, so it's not an issue. As long as things remain deterministic and/or drift slowly enough, no problem.

However, we also check the phase relationship between the captured sines and there comes the issue. Between ADCs on the same ADC board, their phase shift between them within less than 0,1 degree peak to peak within captures and between captures, about 0,02 degrees RMS, with a noise-like shape. This is after removing the baseline phase shift (about 0,5º or so) likely caused by the signal splitter and the input balun of the ADC, and cable mismatch. On the other hand, between ADCs on different ADC boards we observe a rapid phase wander of +-3 degrees.

It is a phase wander, not a delay wander, as it remains constant with ADC input frequency, and it's not a drift, as it averages out to a baseline phase shift which remains constant between captures at the same input frequency. It bounces around aperiodically but not erratically, softly and gracefully dancing from -3 to 3º with respect to the baseline, with a maximum pseudo-oscillation frequency of about 200 Hz (we see mounds and valleys in the phase shift separated by a minimum of 5ms, with a soft, continous transition between them). Again, this phase wander is independent on the input ADC frequency. The higher the frequency the higher the baseline phase shift (linearly related, as there's a small delay) around where the phase dances about, but the wander awlays amounts to about 6de peak to peak independently of the frequency.

The ADCs are not TI parts but they use an architecture similar to some TI parts. The input, sampled at 2457,6 MHz at an intermediate frequency is downconverted to baseband with the ADC's internal downconverter, which employs an NCO clocked at the same ADC sampling clock. We also have to syncrhonize the NCOs, but that seems to work well.

We've thought about what could be causing such a phase wander and we think it might be caused by clock wander between ADC sampling clocks at different ADC boards. We have checked the phase noise of the LMK04828's clock outputs and matches the expected profile and performance. We also measured the output clocks of two ADC boards simultaneously, but as our best scope currently on-hand only goes to 1 GHz, we had to measure a 245,76 MHz clock from each board, 10 times slower than the ADC sampling clock. After LMK04828 synchronization, they end up in phase with neglible delay between them, and there doesn't seem to be any appreciable wander between them. The scope tells us that if there's some wander (low freq. jitter), it's less than 15ps RMS between these divided clocks, but the scope isn't the best for this application and we can't get anything better in the current circumstances.

However, the true clock wander between LMK04828's in different ADC boards could be non-negligible. If the ADC didn't have an NCO that would create delay wander, but with the NCO in place it could also translate to phase wander. We're not seeing the delay wander as the sampled signal is decimated by a factor of 24, but things happening to the NCO which is clocked at the ADC sampling clock could be affecting.

We've seen several TI examples such as TIDA-01021 where you achieve very decent results with LMK04828's and even more PLL loops working together and with ADCs which also have an NCO, so we're not sure about what could be happening in our case. Do you have any clue about what might be happening?

Regards,