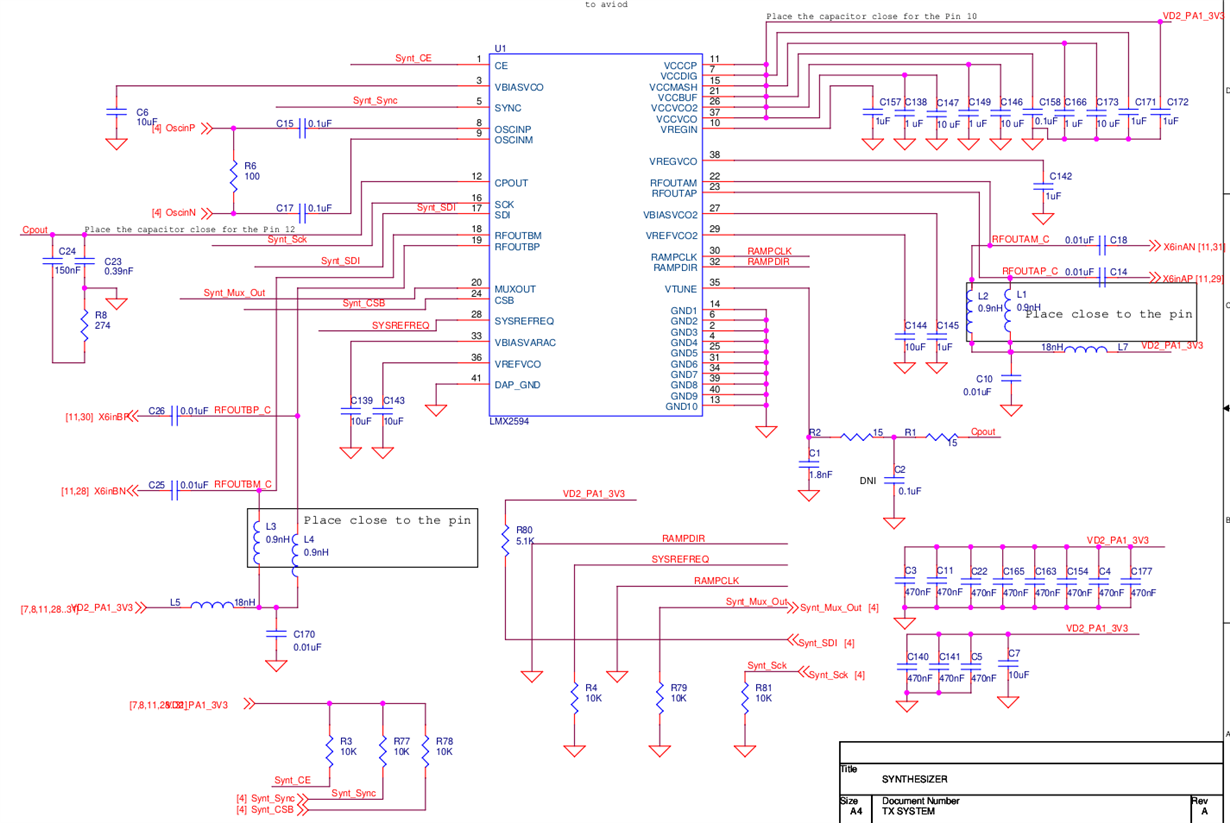

We have designed a transceiver system in which the LO is being generated by LMX2594 at 12.5 GHz output. I have used PLLatinum Simulation Tool to design the loop filter. The filter was originally designed for 20.833 MHz Fosc. The input reference clock is provided by Analog Device's HMC7044. Our design requirement limits the Fosc to integral multiples of 2.604 MHz up to 100 MHz like 10.433 MHz, 20.833 MHz, 41.667 MHz etc. The schematic is attached below-

However, in the actual hardware the performance is not as good as expected. There are 2 types of spurious: 1) around 3kHz offset from carrier and 2) around 150 kHz offset from carrier. The tradeoff in performance is as follows-

1. Lowering Fosc to 2.604 MHz improves 150 kHz offset spurious but deteriorates 3 kHz offset spurious

2. Increasing Fosc to 41.667 improves 3 kHz offset spurious but deteriorates 150 kHz offset spurious.

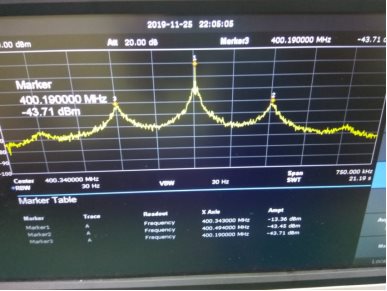

Below is the 150 kHz spurious I am referring to with Fosc=20.833 MHz and OSC_2X enabled ( the frequency has been downconverted by our Rx to suit the spectrum analyser range)-

1. Could you suggest ways to improve the Fout Phase Noise and performance like better filter and schematic design or any other settings in the LMX2594 configuration?

2. How effective is OSC_2X doubler before Fpd and charge pump current to improve PN?

3. The Fout is also seen to drift away from its initial locking frequency with time. What can be the cause and how to improve this?

Thanks

Samarth