Hi Team,

Please advise me on my question bellow.

Can you explain how LMH1983 behaves when it is set into

(1) 00, Always drift lock,

(2) 01, Drift Lock if

(3) 1x, Always Crash Lock

I suppose that in (1)00, “Always Drift lock mode”, LMH1983 smoothly shifts

TOF1 timing and try to align to the input frame regardless input and

output video timing difference.

In (2)01, “Drift lock if” mode, LMH1983 smoothly shifts TOF1 timing and try

to align to the input frame, as long as, input and output video timing

difference is less than two video lines, otherwise, it makes Cras lock.

In (3) 1x, “Always Crash Lock mode”, LMH1983 makes Crash lock,

regardless input and output video timing difference.

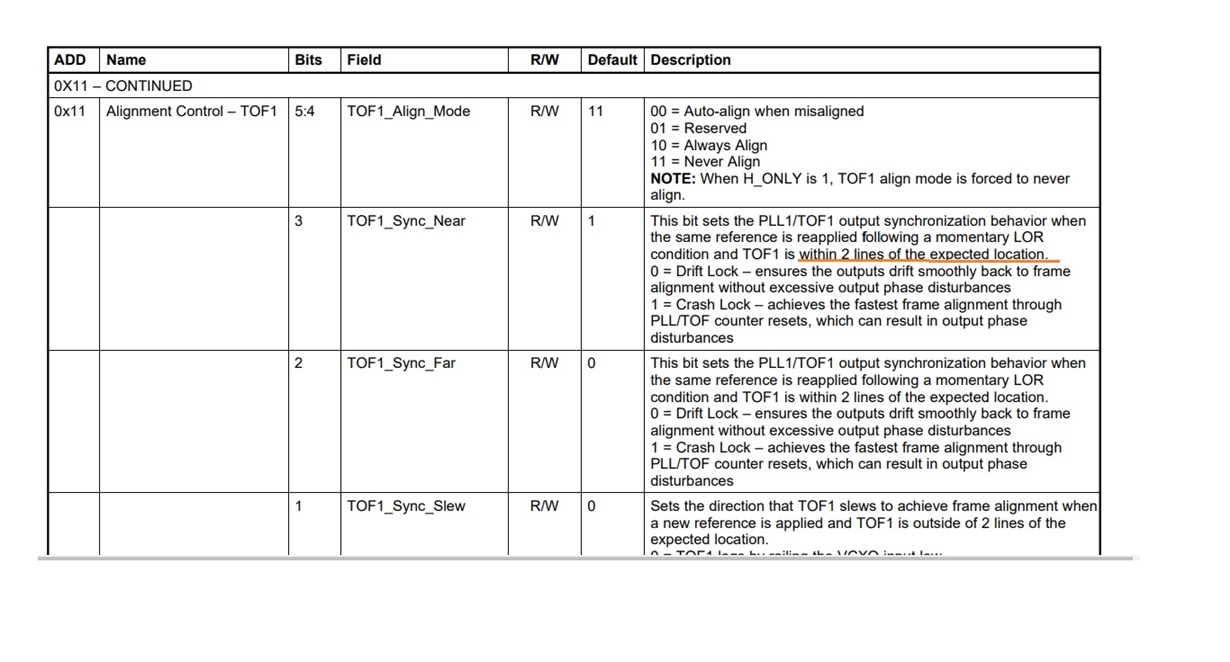

In the meantime, the datasheet express (on Page 28, as shown below)

express differently.

Question: Please let me know which reflects the proper behavior of the LMH1983.

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

This bit sets the PLL1/TOF1 output synchronization behavior

when the same reference is reapplied following a momentary

LOR condition and TOF1 is within 2 lines of the expected location.

00 = Always Drift Lock – ensures the outputs drift smoothly back

to frame alignment without excessive output phase disturbances

01 = Drift Lock if output < (2LOA_window x 27 MHz Clock). Crash Lock

otherwise.

1X = Always Crash Lock – achieves the fastest frame alignment through

PLL/TOF counter resets, which can result in output phase disturbances

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

Mita