Other Parts Discussed in Thread: TIDA-010122, , PLLATINUMSIM-SW

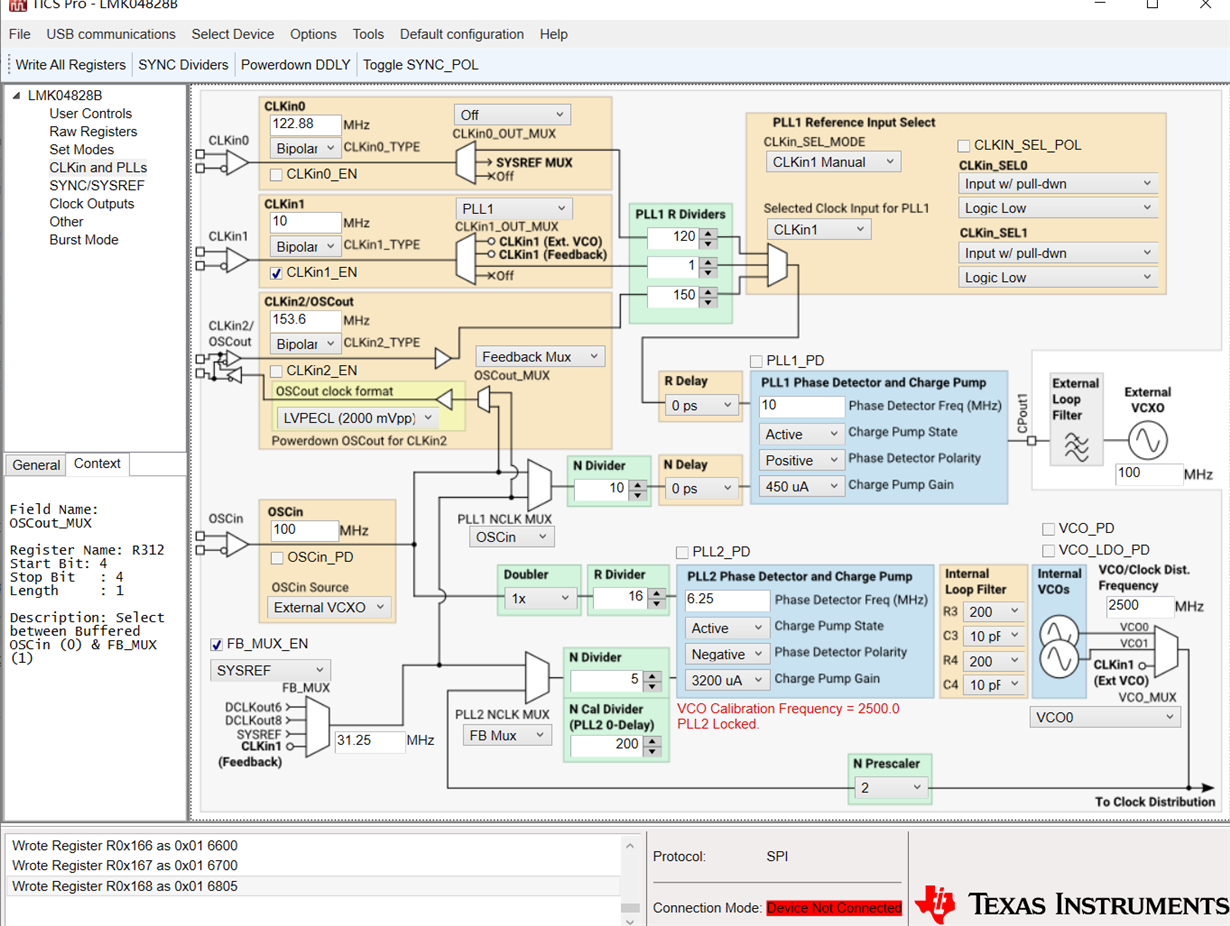

LMK04828B configuration as follows:

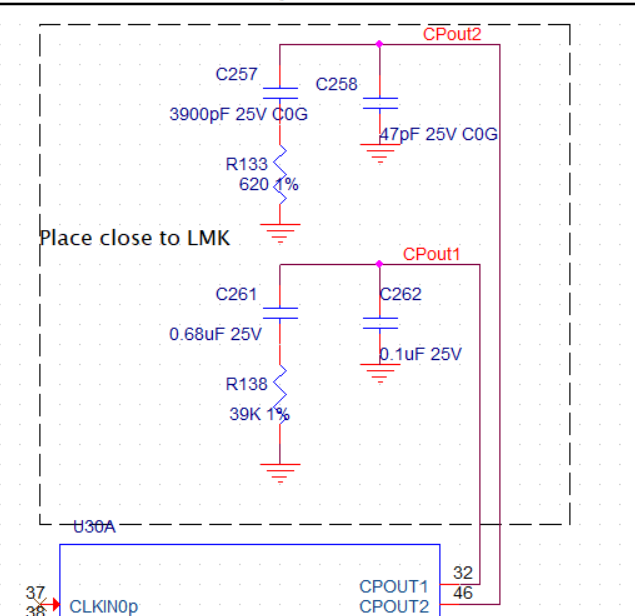

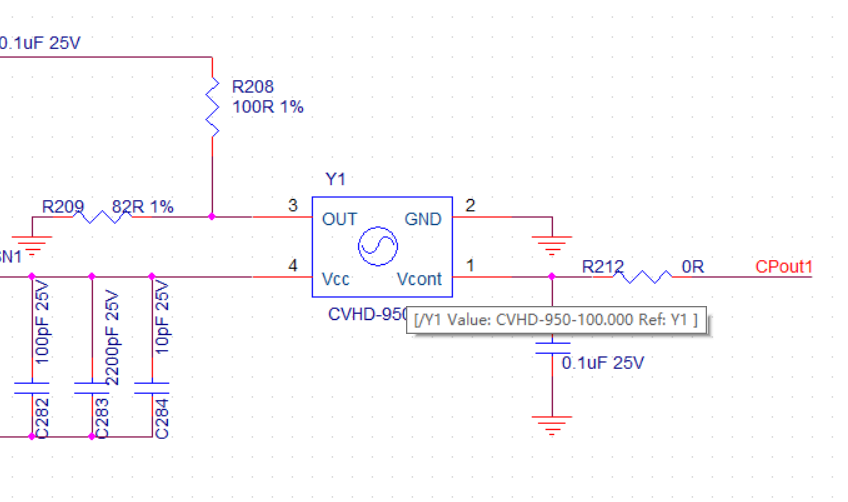

Hardware design refer to TIDA-010122

10MHz input Clkin1, Dual-PLL mode, output frequency: 31.25MHz, 125MHz, 250MHz

Feedback Mux = SYSREF = 31.25MHz

We manufacture up to 15 Boards. Most of them (not all) have the following phenomena:

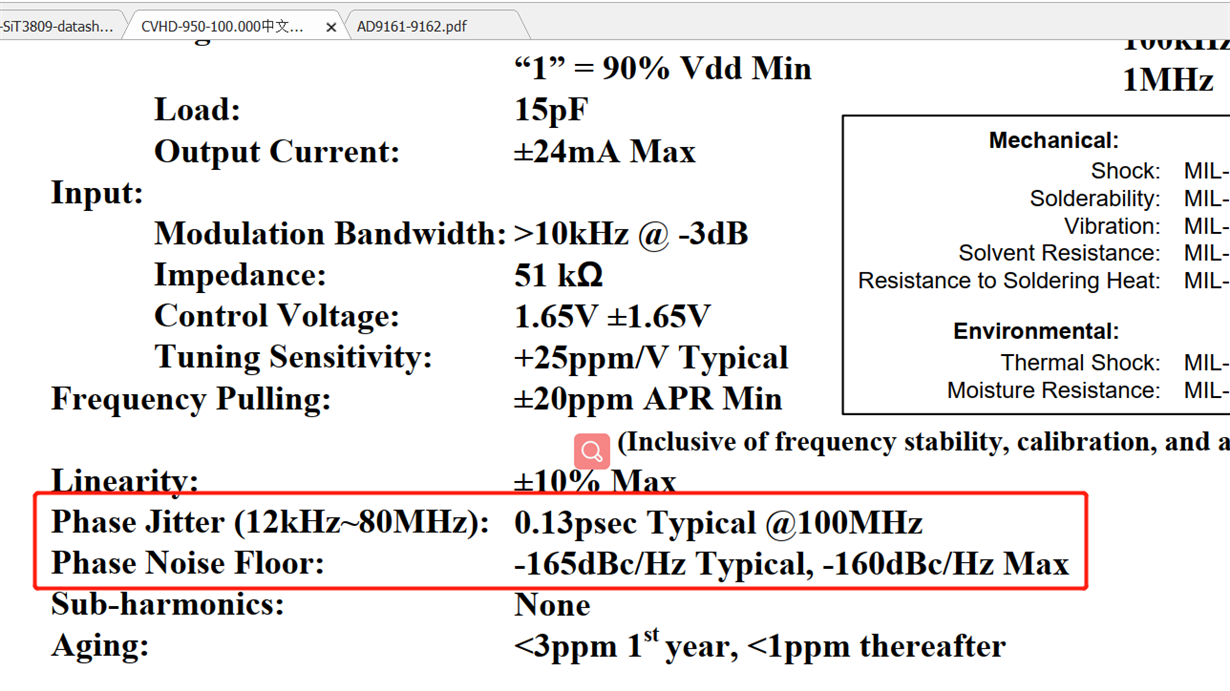

After power these boards, we use a small fan to cool them, the lock-detect led of PLL1 and PLL2 will turn on and remain unchanged. But when we try to use a more powerful fan to cool them (focus on LMK04828B), the lock-detect led of PLL1 will blink and PLL2 lock led will not blink. Then we change to small fan, the PLL1 lock led will gradually keep the lights on.

All these board had been immersed in electron fluoride liquid of 3M.

Obviously, temperature can affect PLL1 locking. Can anyone give me some help? Thanks!