Other Parts Discussed in Thread: LMK04803,

Hello

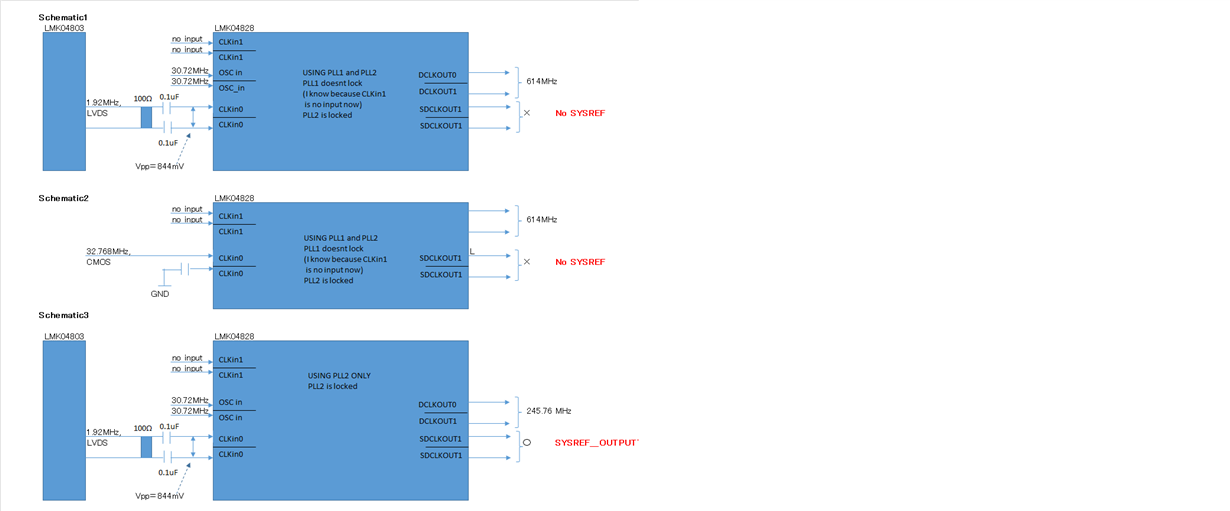

Now I try to "direct sysref mode" but It doesnt work (no output and signal fixed to LOW . input SYNC signal is High.)

My Configuration is as below. (SYSREF signal is conected to Clkin0 )

0x143 0x10 SYNC_MODE

0x139 0x04 SYSREF_MUX,SYSREF CLKin0_MUX

0x147 0x18 CLKin0_OUT_MUX

0x104 0x20 SDCLKoutY_DDLY

0x140 0x07 SYSREF_DDLY_PD,PLSR,PD

0x106 0x30 SDCLKoutY_PD

0x107 0x55 SDCLKoutY_FMT

Would you please tell me something wrong point?

Takeshi